#### Rochester Institute of Technology

### **RIT Digital Institutional Repository**

Theses

1-2014

### **Design for Implementation of Image Processing Algorithms**

Jamison D. Whitesell

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Whitesell, Jamison D., "Design for Implementation of Image Processing Algorithms" (2014). Thesis. Rochester Institute of Technology. Accessed from

This Thesis is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

### **Design for Implementation of Image Processing Algorithms**

by

Jamison D. Whitesell

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Supervised by

Dr. Dorin Patru Department of Electrical and Microelectronic Engineering Kate Gleason College of Engineering Rochester Institute of Technology Rochester, NY January 2014

**Approved By:**

Dr. Dorin Patru Associate Professor – R.I.T. Dept. of Electrical and Microelectronic Engineering

Dr. Eli Saber Professor – R.I.T. Dept. of Electrical and Microelectronic Engineering

Dr. Mehran Kermani Assistant Professor – R.I.T. Dept. of Electrical and Microelectronic Engineering

Dr. Sohail Dianat Department Head – R.I.T. Dept. of Electrical and Microelectronic Engineering

## Dedication

To my family,

without whom none of my success would be possible.

## Acknowledgements

I would like to thank:

Dr. Dorin Patru for giving me the opportunity to be a part of this research and for guidance throughout the thesis process;

Brad Larson, Gene Roylance, and Kurt Bengston for their insight and continued support;

Ryan Toukatly and Alex Mykyta for their research efforts which lay the technical groundwork for this project;

James Mazza, Sankaranaryanan Primayanagam, and Osborn de Lima for providing valuable suggestions during the course of this work;

and my committee members, Dr. Eli Saber and Dr. Mehran Kermani;

## Abstract

Color image processing algorithms are first developed using a high-level mathematical modeling language. Current integrated development environments offer libraries of intrinsic functions, which on one hand enable faster development, but on the other hand hide the use of fundamental operations. The latter have to be detailed for an efficient hardware and/or software physical implementation. Based on the experience accumulated in the process of implementing a segmentation algorithm, this thesis outlines a design for implementation methodology comprised of a development flow and associated guidelines.

The methodology enables algorithm developers to iteratively optimize their algorithms while maintaining the level of image integrity required by their application. Furthermore, it does not require algorithm developers to change their current development process. Rather, the design for implementation methodology is best suited for optimizing a functionally correct algorithm, thus appending to an algorithm developer's design process of choice.

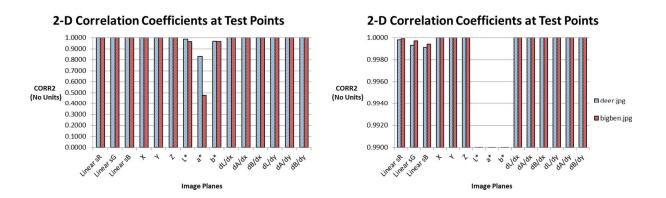

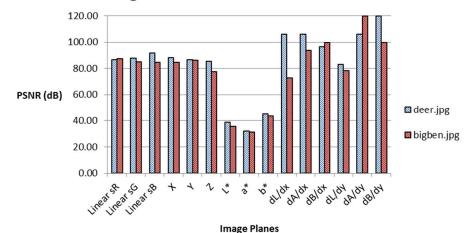

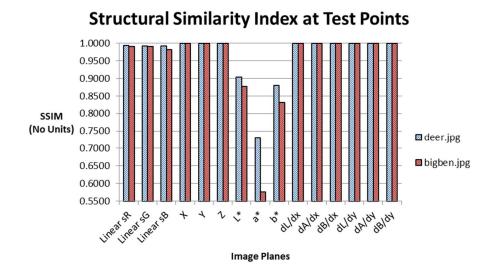

The application of this methodology to four segmentation algorithm steps produced measured results with 2-D correlation coefficients (CORR2) better than 0.99, peak-signal-to-noise-ratio (PSNR) better than 70 dB, and structural-similarity-index (SSIM) better than 0.98, for a majority of test cases.

## **Table of Contents**

| Dedicati  | on                                                   | ii  |

|-----------|------------------------------------------------------|-----|

| Acknow    | edgements                                            | iii |

| Abstract  |                                                      | iv  |

| Table of  | Contents                                             | V   |

| List of F | igures                                               | vii |

| List of S | ymbols                                               | X   |

| Glossary  | ,<br>,                                               | xii |

| Chapter   | 1: Introduction                                      | 1   |

| Chapter   | 2: Background                                        | 5   |

| 2.1       | Related Work                                         | 5   |

| 2.2       | Prior Research Leading to the Multichannel Framework | 8   |

| 2.3       | The GSEG Algorithm as a Test Vehicle                 | 10  |

| Chapter   | 3: Algorithm Modifications                           | 13  |

| 3.1       | Design for Implementation Test Vehicle               | 13  |

| 3.2       | Modifications to the MCF Instruction Set             | 20  |

| Chapter   | 4: Design for Implementation                         | 24  |

| 4.1       | Design for Implementation Flow                       | 24  |

| 4.2       | Design for Implementation Guidelines                 |     |

| 4.3       | General Applicability of the Proposed Methodology    | 29  |

| Chapter   | 5: Implementation of the Test Vehicle                | 31  |

| 5.1       | Conversions between Programming Languages            |     |

| 5.2       | Image Quality Metrics and Validation                 |     |

| 5.3       | Test Setup                                           |     |

| Chapter  | 6: Results and Discussions                               |    |  |  |

|----------|----------------------------------------------------------|----|--|--|

| 6.1      | Validation of Algorithm Modifications                    |    |  |  |

| 6.2      | Cases of Significant Degradation                         | 42 |  |  |

| 6.3      | Logic Utilization, Power Consumption, and Execution Time | 47 |  |  |

| Chapter  | 7: Conclusion                                            | 55 |  |  |

| Referenc | es                                                       | 57 |  |  |

| Appendi  | x A: Hardware and Software Used                          | 59 |  |  |

| Hard     | ware                                                     | 59 |  |  |

| Softv    | vare                                                     | 59 |  |  |

| Appendi  | x B: Color Images                                        | 60 |  |  |

| Appendi  | Appendix C: MATLAB Code for Recording Execution Times62  |    |  |  |

# **List of Figures**

| Figure 2.1: R. Toukatly's Dual-Pipe PR CSC Engine, Reproduced from [2]                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2: A. Mykyta's Multichannel Framework, Reproduced from [3] 10                                                                                                           |

| Figure 2.3: Block diagram of GSEG algorithm, Reproduced from [4] 11                                                                                                              |

| Figure 3.1: A. Mykyta's Generic Instruction Word Format, Reproduced from [3] 21                                                                                                  |

| Figure 3.2: Packet Format, Modified from [3]                                                                                                                                     |

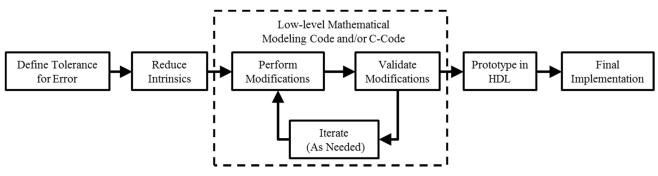

| Figure 4.1: The Design for Implementation Iterative Flow                                                                                                                         |

| Figure 6.1: Two-dimensional correlation coefficients for all modified stages of the GSEG algorithm. The right-hand side shows an enhanced view of the range from 0.99 to 1.00.40 |

| Figure 6.2: Peak signal-to-noise ratios for all modified stages of the GSEG algorithm 41                                                                                         |

| Figure 6.3: Structural similarity indices for all modified stages of the GSEG algorithm. 42                                                                                      |

| Figure 6.4 (LEFT): The GSEG result in the CIE L*a*b* color space                                                                                                                 |

| Figure 6.5 (RIGHT): The MCF result in the CIE L*a*b* color space                                                                                                                 |

| Figure 6.6 (LEFT): The GSEG result in the CIE L*a*b* color space                                                                                                                 |

| Figure 6.7 (RIGHT): The MCF result in the CIE L*a*b* color space                                                                                                                 |

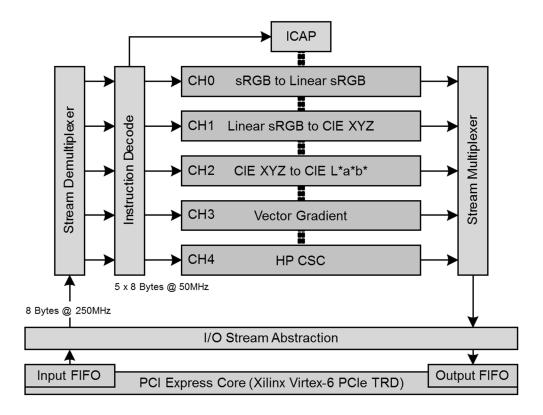

| Figure 6.8: Block Diagram of the MCF with all GSEG Modules, Modified from [3] 45                                                                                                 |

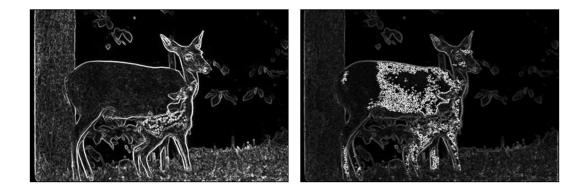

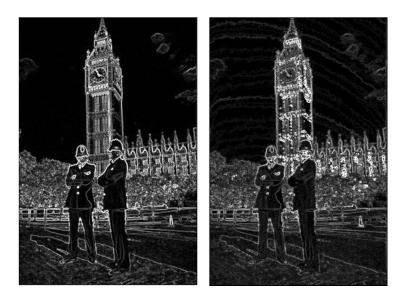

| Figure 6.9 (LEFT): The Edge Map generated by the GSEG algorithm in MATLAB 46                                                                                                     |

| Figure 6.10 (RIGHT): The Edge Map generated from successive modules in the MCF. 46                                                                                               |

| Figure 6.11 (LEFT): The Edge Map generated by the GSEG algorithm in MATLAB 47                                                                                                    |

| Figure 6.12 (RIGHT): The Edge Map generated from successive modules in the MCF. 47                                                                                               |

| Figure 6.13: Block Diagram of the MCF with five channels utilized, Modified from [3].                                                                                            |

| Figure 7.1 (LEFT): The GSEG result in the CIE L*a*b* color space                                                                                                                 |

| Figure 7.2 (RIGHT): The MCF result in the CIE L*a*b* color space | 60 |

|------------------------------------------------------------------|----|

| Figure 7.3 (LEFT): The GSEG result in the CIE L*a*b* color space | 60 |

| Figure 7.4 (RIGHT): The MCF result in the CIE L*a*b* color space | 61 |

## **List of Tables**

| Table 3.1: Supported Instruction Word Opcodes, modified from [3]                  | 22 |

|-----------------------------------------------------------------------------------|----|

| Table 6.1: FPGA Resource Utilization, MCF & PCIe taken with permission from [3]   | 49 |

| Table 6.2: Logic Utilization for MCF Configurations with multiple active channels | 50 |

| Table 6.3: Power Consumption Estimates.                                           | 52 |

| Table 6.4: Comparison of Execution Times.                                         | 53 |

# List of Symbols

| R <sup>'</sup> 8-bit           | Red pixel value in the Standard RGB color space                         |

|--------------------------------|-------------------------------------------------------------------------|

| Ġ'8-bit                        | Green pixel value in the Standard RGB color space                       |

| B'8-bit                        | Blue pixel value in the Standard RGB color space                        |

| R <sup>'</sup> <sub>sRGB</sub> | Red pixel value normalized in the sRGB color space                      |

| $\dot{G_{sRGB}}$               | Green pixel value normalized in the sRGB color space                    |

| B <sup>'</sup> sRGB            | Blue pixel value normalized in the sRGB color space                     |

| <i>R</i> <sub>sRGB</sub>       | Red pixel value in the Linearized sRGB color space                      |

| G <sub>sRGB</sub>              | Green pixel value in the Linearized sRGB color space                    |

| <b>B</b> <sub>sRGB</sub>       | Blue pixel value in the Linearized sRGB color space                     |

| X                              | X pixel value represented in the CIE 1931 XYZ color space               |

| Y                              | Y pixel value represented in the CIE 1931 XYZ color space               |

| Ζ                              | Z pixel value represented in the CIE 1931 XYZ color space               |

| X <sub>n</sub>                 | X component of the CIE XYZ tri-stimulus reference white point           |

| $Y_n$                          | Y component of the CIE XYZ tri-stimulus reference white point           |

| $Z_n$                          | Z component of the CIE XYZ tri-stimulus reference white point           |

| $L^*$                          | Luminance pixel value represented in the CIE 1976 L*a*b* color space    |

| <i>a</i> *                     | First color pixel value represented in the CIE 1976 L*a*b* color space  |

| <i>b</i> *                     | Second color pixel value represented in the CIE 1976 L*a*b* color space |

| x                              | Variable representing an X, Y, or Z pixel value in a function           |

| L* <sup>'</sup>                | Luminance pixel value denoted with a prime to avoid redundancy          |

| a*'                            | Color pixel value denoted with a prime to avoid redundancy              |

| b*'                            | Color pixel value denoted with a prime to avoid redundancy              |

| m                              | Total number of rows of pixels in a given image                         |

| n                              | Total number of columns of pixels in a given image                      |

| k                              | Total number of pixels in an arbitrary dimension of an image            |

| i                                | Present row in a matrix of pixels                                     |

|----------------------------------|-----------------------------------------------------------------------|

| j                                | Present column in a matrix of pixels                                  |

| t                                | Present time (i.e., in a series of sequential operations)             |

| р                                | Pixel value at location given by <i>i</i> and <i>j</i> or by <i>t</i> |

| $g_x(i,j)$                       | Vector gradient calculated in the x direction of an image             |

| $g_{y}(i,j)$                     | Vector gradient calculated in the y direction of an image             |

| g(i,j)                           | Vector gradient calculated in an arbitrary direction based on $k$     |

| f                                | Known good image for comparing result images against                  |

| g                                | Result image being compared against a known good image                |

| r(f,g)                           | Two-dimensional correlation coefficient                               |

| $ar{f}$                          | Mean of known good image                                              |

| $ar{g}$                          | Mean of result image                                                  |

| b                                | Number of bits used to represent a pixel value                        |

| $d_{dx}$                         | Alternate symbol for the vector gradient in the x direction           |

| $\frac{d}{dx}$<br>$\frac{d}{dy}$ | Alternate symbol for the vector gradient in the y direction           |

# Glossary

| ASIC Application-Specific Integrated Circuit |                                                                 |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

|                                              | Application-Specific Integrated Circuit                         |  |  |  |  |

| CIE                                          | International Commission on Illumination                        |  |  |  |  |

|                                              | (Commission Internationale de l'éclairage)                      |  |  |  |  |

| СМҮК                                         | Cyan-Magenta-Yellow-Key                                         |  |  |  |  |

| CORDIC                                       | Coordinate Rotation Digital Computer (Square-rooting Algorithm) |  |  |  |  |

| CORR2                                        | Two-Dimensional Correlation Coefficient                         |  |  |  |  |

| CSC                                          | Color Space Conversion                                          |  |  |  |  |

| DFI                                          | Design for Implementation                                       |  |  |  |  |

| DPR                                          | Dynamic Partial Reconfiguration                                 |  |  |  |  |

| DSP                                          | Digital Signal Processing                                       |  |  |  |  |

| FIFO                                         | First-In-First-Out Buffer                                       |  |  |  |  |

| FPGA                                         | Field Programmable Gate Array                                   |  |  |  |  |

| GSEG                                         | Gradient-Based Segmentation                                     |  |  |  |  |

| HDL                                          | Hardware Description Language                                   |  |  |  |  |

| HP                                           | Hewlett Packard                                                 |  |  |  |  |

| ICAP                                         | Internal Configuration Access Point                             |  |  |  |  |

| IP                                           | Intellectual Property                                           |  |  |  |  |

| L*a*b*                                       | The 1976 CIE L*a*b* Color Space                                 |  |  |  |  |

| MCF                                          | Multichannel Framework                                          |  |  |  |  |

| MEX                                          | MATLAB Executable                                               |  |  |  |  |

| MRI                                          | Magnetic Resonance Imaging                                      |  |  |  |  |

| PC                                           | Personal Computer                                               |  |  |  |  |

| PCI                                          | Peripheral Component Interconnect                               |  |  |  |  |

| PCIe                                         | PCI-Express                                                     |  |  |  |  |

| PR                                           | Partial Reconfiguration                                         |  |  |  |  |

| PRR                                                                 | Partially Reconfigurable Region                                   |  |  |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| PSNR                                                                | Peak Signal to Noise Ratio                                        |  |  |  |

| Reg-bus                                                             | CSC Register Bus                                                  |  |  |  |

| RGB                                                                 | Red-Green-Blue                                                    |  |  |  |

| RR                                                                  | Reconfigurable Region                                             |  |  |  |

| RTL                                                                 | Register Transfer Level                                           |  |  |  |

| sRGB Standard Red-Green-Blue (HP & Microsoft Collaborative Color Sp |                                                                   |  |  |  |

| SSIM                                                                | Structural Similarity Index                                       |  |  |  |

| SRAM                                                                | Static Random-Access Memory                                       |  |  |  |

| TRD                                                                 | Targeted Reference Design                                         |  |  |  |

| Verilog                                                             | Verify-Logic Hardware Description Language                        |  |  |  |

| VHDL                                                                | Very-high-speed integrated circuits Hardware Description Language |  |  |  |

| XYZ                                                                 | The 1931 CIE XYZ Color Space                                      |  |  |  |

### **Chapter 1:** Introduction

Most often the same individual or group of individuals does not perform both: the design of the high-level model of an algorithm and its implementation. Algorithm development typically focuses on achieving functional correctness, which comes at the expense of high computational resources. The goal of implementation, on the other hand, is to achieve maximum efficiency. This means minimal computational resources, low power, and high execution speed. When algorithms are tailored for efficiency, precision is often sacrificed, creating a dichotomy. The lack of cross-disciplinary expertise may result in valuable optimization opportunities to be missed. During the implementation phase of multi-step image processing algorithms, hardware/software engineers may be reluctant to modify the high-level model of the algorithm to improve efficiency, due to their limited imaging science background. For these reasons, this work argues that the selection of implementation-efficient operations and optimal number representations, among other algorithm optimizations, should be performed during the high-level modeling of the algorithm.

Once an image processing algorithm has been passed from the algorithm development phase to the hardware implementation phase, a number of techniques exist for enabling hardware/software engineers to achieve optimal implementations in terms of speed, area, and power consumption [1]. The sequential portions of an algorithm can be pipelined to increase throughput, while other portions that are fundamentally concurrent

can be computed in parallel. Other methods such as selective reset strategies and resource sharing can reduce overall resource utilization and congestion. As the well-known Amdahl's Law can be adapted to this matter, these hardware-centric optimization techniques are theoretically limited by the inherent nature of the algorithm being implemented. In order to maximize the number of possible optimizations, modifications for efficiency should be taken into consideration during the initial development process of the algorithm.

Image processing algorithms are typically developed using a high-level modeling software suite such as MATLAB, Mathcad, or MAPLE. However, these tools don't lend well to creating code that can be considered implementation-efficient or "friendly." An algorithm whose operations can be mapped directly to a Hardware Description Language (HDL) and/or in some cases C-code is considered implementation-friendly. In an effort to bridge the gap between disciplines, much work has been done to facilitate algorithmhardware co-design, as will be discussed in the next chapter. Algorithms developed in the aforementioned high-level programming languages often use intrinsic function calls that buffer the algorithm developer from the detailed calculations, but result in dead-ends for hardware/software designers attempting to identify fundamental operations. Direct translations of these high-level models into implementations result in overly complex and generally inefficient designs. By taking advantage of the optimization opportunities present during the development process of the algorithm, as well as applying proper techniques for efficient hardware realization, a maximally efficient implementation can be reached.

As the continuation of a sponsored research project for Hewlett Packard (HP), the original goal of this work was to further evaluate the use of Field Programmable Gate Arrays (FPGAs) as viable alternatives to Application Specific Integrated Circuits (ASICs). The emergence of Dynamic Partial Reconfiguration (DPR) for FPGAs created the possibility for image processing modules to be effectively swapped with modules of a different functionality at run-time. By foreseeing the potential gains of masking dynamic reconfiguration with active processing, R. Toukatly et al. and A. Mykyta et al. [2, 3] developed a multichannel framework (MCF). A color space conversion (CSC) engine provided by HP was used to initially evaluate this framework. A variety of image processing modules was needed to further evaluate its viability.

A high-level model of a gradient-based segmentation (GSEG) algorithm [4], also provided by HP, was chosen to evaluate the framework due to the number of different image processing techniques inherent in the automatic segmentation of a color image. During the process of converting this GSEG algorithm into an implementation, numerous difficulties were experienced which led to the proposal of a design methodology for algorithm implementation. Rather than just implement the algorithm directly for the purpose of evaluating the framework, it was used as a test vehicle to take advantage of the optimization opportunities inherent in the development phase of the algorithm. As a result, this work presents a set of guidelines that, when followed during the algorithm development phase, result in implementation-efficient and friendly algorithms. When paired with a corresponding design flow, a methodology is formed that is coined Design for Implementation (DFI). This thesis demonstrates the DFI design methodology using the GSEG algorithm as a test vehicle and leverages the resulting image processing modules to further evaluate the multichannel framework. In the following chapter, the background of this work presented, as well as several other research works that involve methods for realizing efficient implementations. In Chapter 3, the algorithm modifications that lead to the development of the DFI methodology are presented in significant detail. Chapter 4 describes the proposed methodology in two parts: the design flow and the accompanying guidelines. With the methodology defined, Chapter 5 describes the development process and the test setup used for implementing and evaluating the image processing modules. Chapter 6 presents and discusses the results obtained from the image processing modules and, also, the results from their use as an image processing pipeline. Finally, Chapter 7 concludes the research and also presents potential future work.

## Chapter 2: Background

#### 2.1 Related Work

The goal of achieving an efficient design implementation is paramount to drive cost down. This requires design parameters such as execution time, silicon area, and power consumption to be reduced. A number of methods for optimizing these parameters for FPGA based implementations of algorithms have been used over recent years [1]. Exploring optimization at an even higher level of abstraction, the functional partitioning of a design has yielded improvements compared to structural partitioning [5]. Additionally, partitioning, while leveraging the dynamic partial reconfiguration feature, has been shown to increase speedup [3]. These techniques, however, are all limited by the optimizations inherent within the algorithm presented to the hardware/software engineer.

The corollary is that the algorithm be tailored for hardware before being presented to the engineer who is responsible for implementation. This requires that the algorithm be optimized by an experienced developer or an automated tool – such as a compiler. D. Bailey and C. Johnston presented eleven algorithm transformations for obtaining efficient hardware architectures [6]. While a number of these techniques such as loop unrolling, strip mining, and pipelining could be handled by compilers, other practices such as operation substitution and algorithm rearrangement require a human developer with extensive knowledge of a given algorithm. An automated compiler for generating optimized HDL from MATLAB was developed by M. Haldar et al. [7]. By using the automated compiler to optimize the MATLAB code, improvements in implementation parameters were shown as reductions in resource utilization, execution time, and design time. Although in some cases the execution time was longer, the authors argued that the compiler significantly reduced the design time. It could be further argued that an engineer would spend less time optimizing the generated HDL than if he were starting from scratch. Regardless, numerous gains were reported and were even increased with the integration of available Intellectual Property (IP) cores, which are typically provided by the FPGA manufacturer in the synthesis tools. These IP cores are capable of targeting specific structures within an FPGA, leading to optimal use of resources.

In the case of image processing algorithms, the major design constraint is the tradeoff between parameters such as speed, area, and power consumption on one hand, and image quality on the other hand. The automated HDL from [7] produced identical results to that of the original MATLAB algorithm, in terms of image quality. While this result is ideal, it suggests that there are further optimizations that could be made, since many applications exist that do not require perfect image quality. Other research by G. Karakonstantis et al. [8] proposes a design methodology which enables iterative degradation in image quality – namely, Peak Signal to Noise Ratio (PSNR) – while undergoing voltage scaling and extreme process variations. By defining an acceptable level of image quality and identifying the portions of the algorithm that contribute most significantly to the quality metric, the voltage supply can be scaled and process variations.

can be simulated until the acceptable image quality threshold is reached. Theoretically, the iterative approach ensures that an optimal design for the application is obtained.

It is apparent that additional gains can be made if cross-disciplinary collaboration can be facilitated. Bridging the gap between algorithm developers and hardware/software engineers to enable co-design is not a new idea. In fact, considerable research has been done to enable collaborative design based on task dependency graphs. Research by K. Vallerio and N. Jha [9] created an automated tool to extract task dependency graphs from standard C-code, therefore supporting hardware/software co-synthesis. Vallerio and Jha argued that large gains could be made in system quality at the highest levels of design abstraction, where major design decisions can have major performance implications [9].

The use of these task dependency graphs to generate synthesizable HDL was explored by S. Gupta et al. [10]. In this work, the *SPARK* high-level synthesis framework was developed to create task graphs and data flow graphs from standard C, with the ultimate result being synthesizable Register Transfer Level (RTL) HDL code. In addition to generating a hardware description, code motion techniques and dynamic variable renaming are used to work toward an optimal solution [10]. Another hardware/software co-design methodology and tool, coined *ColSpace* after the "collaborative space" shared between hardware and algorithm designers, was developed by J. Huang and J. Lach [11]. By using task dependency graphs to describe both the algorithm, and the hardware system, the tool acts as an interface for co-optimization. This work also presents an automated process for evaluating image quality compromised by transforms and the subsequent tradeoff between utilization and performance [11].

#### 2.2 Prior Research Leading to the Multichannel Framework

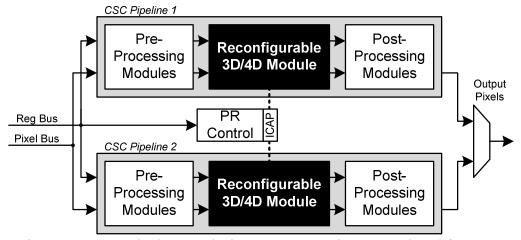

Previous generations of this research project evaluated several different dynamic partial reconfiguration (PR) techniques in FPGAs using a CSC engine provided by HP. The CSC engine is a multi-stage, pipelined architecture capable of converting color images to a desired color space via pre-computed look-up tables. Originally, two main conversion stages – one for three-dimensional inputs and one for four-dimensional inputs – existed sequentially in the pipeline. This architecture lent well to DPR as only one module was needed based on the number of dimensions presented at the input. As a result, a PR region was defined within the engine such that it could be reconfigured for 3D or 4D processing, as seen in Figure 2.1. Here, 3D processing would be resulting in a color space such as RGB, whereas 4D processing would result in a color space such as Cyan-Magenta-Yellow-Key (CMYK).

R. Toukatly et al. first investigated different techniques capable of hiding the delays associated with the configuration operation [2]. By pairing the FPGA with a host processor via a PCI-Express (PCIe) interconnect, the capability of high throughput image processing was added to the CSC engine. In one of the implementations from this work, see Figure 2.1, two separate CSC engines were instantiated enabling the overlapping of processing and reconfiguration. However, since the configuration times were negligible compared to the processing times for larger images, only minimal speedups were achieved. The best case speedups were shown as configuration time and processing time converged to similar

durations. This research laid the groundwork for the development of the multichannel framework.

Figure 2.1: R. Toukatly's Dual-Pipe PR CSC Engine, Reproduced from [2].

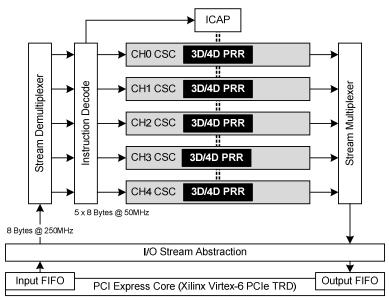

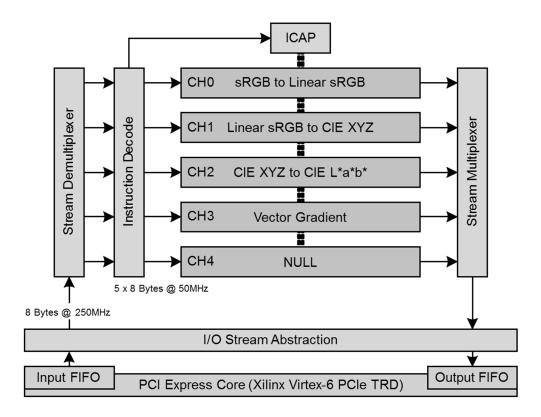

Using the dual-pipeline latency hiding method from Figure 2.1 as a starting point, A. Mykyta et al. developed a generic framework allowing for multiple processing instances to operate simultaneously [3]. To facilitate concurrent and independent processing as well as reconfiguration, five logically isolated channels were defined. In addition to creating an instruction word format, the authors created an input/output abstraction layer to allow data to be fed-to and read-from each processing channel within a 20 ns period. These additions to the dual-pipeline design led to major improvements by allowing more than one channel to perform image processing operations at a time. Both the PR and processing operations were scheduled using a custom text file format that explicitly called out which operations were to be performed and by which channels. These scripts were coined MCF job scripts by the authors. The multichannel framework is presented in Figure 2.2, and shows the numerous changes made to the dual-pipeline design [3]. Namely, the CSC Register Bus (Reg-bus) was eliminated from the design, allowing for data to be multiplexed into the various channels. Another important aspect is that only one Internal Configuration Access Port (ICAP), which controls the bit-streams used for reconfiguring the modules, is available for a PR operation at any time.

Figure 2.2: A. Mykyta's Multichannel Framework, Reproduced from [3].

### 2.3 The GSEG Algorithm as a Test Vehicle

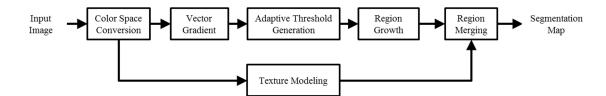

Mentioned previously in the Introduction, a color image segmentation algorithm was chosen to evaluate and validate the framework. This algorithm was therefore used to as a test vehicle for the DFI design methodology. The GSEG algorithm is comprised of a number of steps, some of which exhibit concurrency and others which are iterative. A high-level block diagram of the GSEG algorithm is shown below in Figure 2.3, but does not show the iterative nature of the region growth and region merging processes.

Figure 2.3: Block diagram of GSEG algorithm, Reproduced from [4].

The segmentation algorithm begins with a color space conversion from the sRGB color space to the 1976 CIE L\*a\*b\* color space. This conversion is necessary because the CIE L\*a\*b\* color space models more closely the human visual perception [4] than the sRGB color space – which was designed as a device-independent color definition with low overhead [12]. The use of the CIE L\*a\*b\* space as the basis for creating the edge map produces segmentation maps that more closely resemble those generated by humans [4]. This color space conversion can be partitioned into three smaller steps. The first two steps convert the 8-bit sRGB pixels into linearized sRGB values, followed by the conversion to CIE XYZ values. Finally, the CIE XYZ values transformed into 8-bit CIE L\*a\*b\* values. The conversion from linear sRGB to CIE XYZ uses constants derived from a Bradford chromatic adaptation [13]. These transforms are presented in detail in the next chapter.

The vector gradients are calculated next based on the CIE L\*a\*b\* color image. Each color plane has two corresponding gradients, one in the x direction and another one in the y direction. An edge map is created by combining all six vector gradients into one edge map. The edge map is used to generate adaptive thresholds and to seed the initial regions of the image. The region growth and region merging processes are iterative, but the number of iterations to be performed is adjustable via segmentation parameters. The final region map is merged with a texture model – based on local entropy filtering – to produce a segmentation result. The segmentation map consists of clusters of similar pixels, deemed so based upon color, texture, and spatial locale relative to edges.

The overall process of automatic image segmentation has a variety of applications, including video surveillance and medical imaging analysis [4]. Two specific examples of these applications, respectively, would be the identification of a camouflaged object on the ground in an aerial photograph and the identification of potentially cancerous tissue in a magnetic resonance imaging (MRI) scan. This thesis presents modifications to the color space conversion and vector gradient steps of the segmentation algorithm as test-beds for the development and validation of the DFI methodology.

## **Chapter 3:** Algorithm Modifications

#### 3.1 Design for Implementation Test Vehicle

Before any modifications are made to the algorithm, all high-level intrinsic functions must be recoded, i.e. replaced with explicit known fundamental operations. This step is essential for an implementation-friendly design, and for one that can be translated to any implementation platform. There may be cases where high-level function calls can map directly to a specific intellectual property (IP) core of a given synthesis tool, however the number of these cases is most likely small. It is, however, expected that basic arithmetic operations are readily available as IP cores for a variety of synthesis tools. For the modifications to our GSEG algorithm, the knowledge of available IP cores within the Xilinx software suite was critical [14]. In this chapter, we present the modifications to the GSEG algorithm in "low-level" MATLAB code, which means that all high-level intrinsic functions have been recoded.

Our algorithm begins with a device-independent color definition of an image in the sRGB color space [12]. Each pixel consists of three 8-bit color values – red, green, and blue values. The first step in converting between color spaces is to normalize these pixel values. This is done by dividing each color value by the maximum possible value in the range, as seen in the group of Equations 3.1a. This step results in values between zero and one, which require either floating-point or fixed-point representation. Since the floating-point representation of numbers is more complex than the fixed-point representation, and

requires special floating-point units for processing, fixed-point representation is chosen. As a result and as shown in Equations 3.1b, normalization can be removed.

$$R'_{sRGB} = R_{8bit} \div 255.0$$

$$G'_{sRGB} = G_{8bit} \div 255.0$$

$$B'_{sRGB} = B_{8bit} \div 255.0$$

$$R'_{sRGB} = (R_{8bit} \div 255.0)256.0 \cong R_{8bit}$$

$$G'_{sRGB} = (G_{8bit} \div 255.0)256.0 \cong G_{8bit}$$

$$B'_{sRGB} = (B_{8bit} \div 255.0)256.0 \cong B_{8bit}$$

(3.1b)

In the original algorithm, a piecewise-wise transform follows the normalization step which results in linear sRGB values. Note that in Equations 3.2a the normalized pixel values are compared to a fractional number less than one. The pixel values in our modified algorithm are 8-bit integers at this stage, and must be compared to a value on the same scale. In Equations 3.2b, the fractional number 0.03928 has been scaled up by  $2^8$  in order to make a valid comparison. In the first alternative of the if-clause described in Equations 3.2a, a division is required. Regardless of how this division is implemented – whether by repeated subtraction or by successive right shifts while checking that the remainder is larger than the divisor – it is a time consuming step. Knowing that a bit shift to the right by one place is effectively a division by two, this stage can also be removed by accepting an approximation. If the constant 12.92 is rounded to 16.0, the division can be replaced by four successive shifts to the right. With the division step removed completely, the second case of the piece-wise function becomes our focus.

In the second case of the if-clause, the exponent of 2.4 can be distributed to the numerator and denominator by using basic algebraic manipulation and exponentiation identities. To raise a number to the exponent of 2.4 is not a standard operation and requires a relatively large amount of custom design time. By approximating this exponent with 2.5 and using another exponentiation identity, raising an arbitrary number to the exponent of 2.5 becomes the product of the number's square and square root. Squaring a number is effectively a multiplication with itself and square rooting can be implemented via the available CORDIC IP core [14]. Looking at the denominator, the division by a constant can be replaced with a multiplication by the inverse of the constant. Since the inverse of the constant is less than one, it is scaled up by  $2^8$  so that integer multiplication can be performed. Finally, focusing on the numerator, the constant being added must be scaled by  $2^8$  to match the scaling already applied to the 8-bit sRGB values. The piece-wise function after the application of these modifications is shown in Equations 3.2b.

$$If R'_{sRGB}, G'_{sRGB}, B'_{sRGB} \leq 0.03928$$

$$R_{sRGB} = R'_{sRGB} \div 12.92$$

$$G_{sRGB} = G'_{sRGB} \div 12.92$$

$$B_{sRGB} = B'_{sRGB} \div 12.92$$

else if  $R'_{sRGB}, G'_{sRGB}, B'_{sRGB} > 0.03928$

$$R_{sRGB} = \left[ \frac{\left( R'_{sRGB} + 0.055 \right)}{1.055} \right]^{2.4}$$

$$G_{sRGB} = \left[ \frac{\left( G'_{sRGB} + 0.055 \right)}{1.055} \right]^{2.4}$$

$$B_{sRGB} = \left[ \binom{B'_{sRGB} + 0.055}{1.055} \right]^{2.4}$$

$$If R'_{sRGB}, G'_{sRGB}, B'_{sRGB} \leq 10$$

$$R_{sRGB} = R'_{sRGB} \gg 4$$

$$G_{sRGB} = G'_{sRGB} \gg 4$$

$$B_{sRGB} = B'_{sRGB} \gg 4$$

else if  $R'_{sRGB}, G'_{sRGB}, B'_{sRGB} > 10$

$$R_{sRGB} = \left(R'_{sRGB} + 14\right)^2 \sqrt{\left(R'_{sRGB} + 14\right)} (56.0)$$

$$G_{sRGB} = \left(G'_{sRGB} + 14\right)^2 \sqrt{\left(G'_{sRGB} + 14\right)} (56.0)$$

$$B_{sRGB} = \left(B'_{sRGB} + 14\right)^2 \sqrt{\left(B'_{sRGB} + 14\right)} (56.0)$$

With the first transform in the color conversion process modified, the conversion from the linear sRGB color space to the CIE XYZ color space follows next [12]. As shown in Equation 3.3a, the RGB values are arranged as a column vector and pre-multiplied by a 3x3 matrix of constants. In order to facilitate integer arithmetic, all elements of the constant matrix are scaled by a factor of  $2^{12}$ . With additional down scaling implied in Equation 3.3b, the results of this transform are comparable to the original algorithm with a scaling

factor of 2<sup>16</sup>. As can be seen, there is not much else that can be done to this stage to make it more implementation-friendly. Matrix multiplication is easily mapped to an FPGA via the use of multiply-accumulate operations, a standard method in digital signal processing (DSP). Rather than creating our own custom core to implement this operation, an existing IP core has been used and our overall design time has been shortened.

$$\begin{bmatrix} X \\ Y \\ Z \end{bmatrix} = \begin{bmatrix} 0.4361 & 0.3851 & 0.1431 \\ 0.2225 & 0.7169 & 0.0606 \\ 0.0139 & 0.0971 & 0.7141 \end{bmatrix} \begin{bmatrix} R_{sRGB} \\ G_{sRGB} \\ B_{sRGB} \end{bmatrix}$$

(3.3a)

$$\begin{bmatrix} X \\ Y \\ Z \end{bmatrix} = \begin{bmatrix} 1786 & 1577 & 586 \\ 911 & 2936 & 248 \\ 57 & 397 & 2924 \end{bmatrix} \begin{bmatrix} R_{sRGB} \\ G_{sRGB} \\ B_{sRGB} \end{bmatrix}$$

(3.3b)

Once the pixel values are converted to corresponding values in the CIE XYZ color space, the final conversion to the CIE L\*a\*b\* color space is performed [13]. Note that the following constants – based on a reference white point – are needed for this transform:  $X_n = 0.964203$ ,  $Y_n = 1.000$ , and  $Z_n = 0.824890$ . Equations 3.4a, 3.5a, and 3.6a, show that the X, Y, and Z values from the previous transformation step need to be divided by these constants. In the case of  $Y/Y_n$ , the constant is one and no division is required. For the other two cases, division could be replaced by a multiplication with the inverted and scaled up constants. However, since the inverted constants are approximately one, we have chosen to eliminate this step completely. These modifications are captured in Equations 3.4b, 3.5b, and 3.6b.

$$L^* = 116 f\left(\frac{Y}{Y_n}\right) - 16 \tag{3.4a}$$

$$L^* = 116 f(Y) - 16 \tag{3.4b}$$

$$a^* = 500 \left[ f\left(\frac{X}{X_n}\right) - f\left(\frac{Y}{Y_n}\right) \right]$$

(3.5a)

$$a^* = 500 [f(X) - f(Y)]$$

(3.5b)

$$b^* = 200 \left[ f\left(\frac{Y}{Y_n}\right) - f\left(\frac{Z}{Z_n}\right) \right]$$

(3.6a)

$$b^* = 200 [f(Y) - f(Z)]$$

(3.6b)

Function f(x) is a piece-wise function [13] and is given in Equation 3.7a. Since the input values to this step are scaled by a factor of  $2^{16}$ , the constant value that the input values are compared against must also be scaled by the same factor – which is a similar modification to the one performed in Equations 3.2a. In the first case of Equation 3.7a, a cube root operation is required. To create a custom core to perform this operation would be time consuming and there are no pre-existing Xilinx IP cores for this operation. Using a set of basic algebraic manipulations, the cube root operation can be replaced by the product of multiple square root iterations, as shown in Equation 3.7b. To handle the second case of Equation 3.7a the constant 7.787 can be rounded to 8.0, which effectively replaces the multiplication with a three bit-shifts to the left. The addition of a constant value must be scaled by  $2^{16}$  in order to match the scaling already applied to the input value. These changes are shown in Equation 3.7b.

$$f(x) = \begin{cases} (x)^{1/3}, & if > 0.008856\\ 7.787(x) + \frac{16}{116}, & if \le 0.008856 \end{cases}$$

(3.7a)

$$f(x) = \begin{cases} (x)^{1/4} (x)^{1/16}, & if > 580 \\ (x \gg 3) + 9040, & if \le 580 \end{cases}$$

(3.7b)

The resulting CIE L\*a\*b\* pixel values are finally scaled to 8-bit integer values using equations 3.8 and 3.9. Note that the results from equations 3.4a, 3.5a, and 3.6a have been labeled with apostrophes to avoid duplicated symbols. For Equation 3.8, the division by 100 can be combined with the multiplication by 255, resulting in a multiplication by 26 – not shown. The addition of a constant needs no modifications in Equations 3.9.

$$L^* = 255 \left( \frac{L^{*'}}{100.0} \right) \tag{3.8}$$

$$a^* = a^{*'} + 128.0$$

$b^* = b^{*'} + 128.0$  (3.9)

Once the color space conversion is completed, the vector gradients of each color plane are calculated. As mentioned in the previous chapter, two vector gradients must be computed for each color image plane. The gradient calculation is basically a difference calculation between neighboring pixels, and is shown in Equations 3.10 and 3.11. The division by two is avoided by scaling both cases of the piecewise function by two. This scaling factor can be removed when the results are imported into MATLAB, preserving the precision required by this stage. By inspection, the operations performed to calculate the gradient in the x direction are nearly identical to those used for the y direction. The only differences are the variables that are indexed and the limits m and n. For implementation, it is important to note that the image cannot be indexed bi-directionally as it would in MATLAB. The input pixels must be loaded sequentially, and their relative position in time is referenced to t. By pre-arranging the CIE L\*a\*b\* results in both a row-major format and also a column-major format, one design can be used for both directions of the vector gradient. The only additional point of consideration is that the number of

rows *m* or columns *n* must be specified in conjunction with the input format of the image. By modifying the instruction set of the framework (MCF), a custom user instruction has been added to load the appropriate value, which is denoted by k in Equation 3.12, and discussed in more detail in the next section.

In the equations below, let  $g_x$ , and  $g_y$  be the gradients in the x and y directions of an **m** by **n** image.

Furthermore, let  $\mathbf{i}$  and  $\mathbf{j}$  be row and column indices, and  $\mathbf{p}$  be a pixel value at a location wrt  $\mathbf{i}$  and  $\mathbf{j}$  or wrt a time  $\mathbf{t}$ .

$$g_{x}(i,j) = \begin{cases} p(i+1,j) - p(i,j), & \text{for } i = 1,n \\ \left[\frac{p(i+1,j) - p(i-1,j)}{2}\right], \text{otherwise} \end{cases}$$

(3.10)

$$g_{y}(i,j) = \begin{cases} p(i,j+1) - p(i,j), & \text{for } j = 1,m \\ \left[\frac{p(i,j+1) - p(i,j-1)}{2}\right], \text{ otherwise} \end{cases}$$

(3.11)

$$g_{y}(i,j) = \begin{cases} [p(t+1) - p(t)] \ll 1, & \text{for } t = 1, k \\ [p(t+1) - p(t-1)], & \text{otherwise} \end{cases}$$

(3.12)

### 3.2 Modifications to the MCF Instruction Set

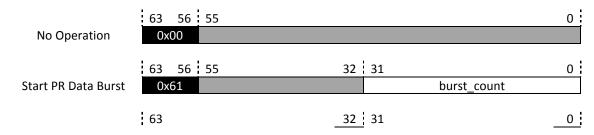

One of the major improvements A. Mykyta made to R. Toukatly's Dual-Pipe Framework was the implementation of an instruction-based interface and a corresponding instruction set [3]. This interface organized input data into 8-byte packets which served as instructions or bursts of raw data, allowing for minimum overhead when transferring large

amounts of data. The generic instruction word format, seen in Figure 3.1, was built to meet requirements for PR and the HP CSC engine, while also allowing for custom user actions to be added in the future.

| 63                  | 62          | 61                | 60 56     | 55 32        | 31 0                                                |

|---------------------|-------------|-------------------|-----------|--------------|-----------------------------------------------------|

| User<br>Instruction | Burst Start | PR<br>Instruction | Operation | [Don't Care] | Burst Count<br>(Required if <i>Burst Start</i> = 1) |

| 1                   | 1           | 1                 | 5         | 24           | 32                                                  |

Figure 3.1: A. Mykyta's Generic Instruction Word Format, Reproduced from [3].

Leveraging the flexibility of the instruction word format, a new instruction word was created for the vector gradient modules. The custom user instruction *Ld Gradient Counter* is automatically sent after the *Flush MCF* and *Channel Sync* commands when the vector gradient processing module is specified in the MCF job script. This command loads a register in the custom user circuit with the height or width, in pixels, of the image being processed. This value was denoted by k in the previous section and is required to trigger special cases of subtraction when the edges of the image are being processed. By modifying the instruction set to add this capability to the user circuit, one vector gradient module was able to be used for both the x direction and y direction gradients.

The various operations built into the instruction set were separated into nonprocessing commands and CSC commands. The instruction added during the course of this work has been classified as a custom command, as it does not pertain to HP's CSC engine, a PR operation, or other routine channel control operations. A summary of all current MCF instructions is presented in Table 3.1, with the custom command appended to the instruction words from the work of A. Mykyta et al..

| Bit Position             | 63                  | 62             | 61                | 60 56     |                     |

|--------------------------|---------------------|----------------|-------------------|-----------|---------------------|

|                          | User<br>Instruction | Burst<br>Start | PR<br>Instruction | Operation | Resulting<br>Opcode |

| Non-Processing Commands: |                     |                |                   |           |                     |

| No Operation             | 0                   | 0              | 0                 | 0x0       | 0x00                |

| Start PR Burst Data      | 0                   | 1              | 1                 | 0x1       | 0x61                |

| Flush MCF                | 0                   | 0              | 0                 | 0x2       | 0x02                |

| Channel Sync             | 0                   | 0              | 0                 | 0x8       | 0x08                |

| CSC Commands:            |                     |                |                   |           |                     |

| Reg-Bus Write            | 1                   | 0              | 0                 | 0x1       | 0x81                |

| Start Pixel Burst        | 1                   | 1              | 0                 | 0x2       | 0xC2                |

| Custom Commands:         |                     |                |                   |           |                     |

| Ld Gradient Counter      | 1                   | 1              | 0                 | 0x5       | 0x85                |

Table 3.1: Supported Instruction Word Opcodes, modified from [3].

The corresponding packet format for the *Ld Gradient Counter* custom instruction word is shown in Figure 3.2. The packet format is very similar to a *Start PR Data Burst* instruction or a *Start Pixel Burst Instruction*. The similar format allowed for a very quick and effortless implementation of the new instruction. The modified packet format diagram is included for completeness and shows how all 8-bytes are used for each instruction. Note that gray areas in the figure represent bits that are unused.

| PR Burst Data       | pr_w                | ord_1               | pr_wo               | ord_0               |

|---------------------|---------------------|---------------------|---------------------|---------------------|

| Flush MCF           | 63 56 55<br>0x02    |                     |                     | 0                   |

| Channel Sync        | 63 56 55<br>0x08    |                     |                     | 4 3 0<br>channel_id |

| Register Write      | 63 56 55 50<br>0x81 | 49 32<br>reg_addr   | 31<br>reg_          | 0<br>data           |

| Start Pixel Burst   | 63 56 55<br>0xC2    | 32                  | 31<br>burst_        | 0<br>count          |

| Pixel Burst Data    | 63 48<br>csc_data_3 | 47 32<br>csc_data_2 | 31 16<br>csc_data_1 | 15 0<br>csc_data_0  |

| Ld Gradient Counter | 63 56 55<br>0x85    | 32                  | 31pixel             | 0<br>count          |

Figure 3.2: Packet Format, Modified from [3].

## **Chapter 4: Design for Implementation**

In the previous chapter, the first steps of the GSEG algorithm were modified to achieve an efficient implementation in an FPGA. The design flow used during this process was documented and a set of design guidelines were generated from observations. The design flow and guidelines have been paired to develop a general methodology for tailoring algorithms for implementation. In this chapter, the Design for Implementation (DFI) methodology is presented in detail.

#### 4.1 Design for Implementation Flow

In order to justify or validate the algorithm modifications presented in the previous chapter, a metric is needed to observe and evaluate changes in the resulting image. With a metric selected, a threshold is chosen based on what is considered acceptable image degradation for the given application. The selection of image quality metrics and the definition of tolerable error serve as the initial step in the DFI flow, which is illustrated in Figure 4.1. The image quality metrics used to evaluate the GSEG algorithm modifications are discussed in more detail in the next chapter.

Figure 4.1: The Design for Implementation Iterative Flow.

As mentioned in the Introduction, the next step in the implementation process of an algorithm is to replace the intrinsic functions. The reduction of these intrinsic functions to fundamental operations, or low-level code, is a vital step since any HDL code needs to be written in terms of these operations. The low-level code serves as a basis for justifying all modifications made to the original algorithm and is recommended to be written in the same high-level programming language as the original image processing algorithm. Next, the conversion of the low-level algorithm to C-code is performed. This step is not absolutely necessary, but can be used to generate a bit-exact model to compare with future HDL results. Finally, functions for different image quality metrics can also be easily written in these languages, may even be intrinsic, or exist already.

Once the sequence of fundamental operations has been detailed in low-level code or C-code, the operations are partitioned into pipeline stages. These pipeline stages represent a series of operations that can each be performed within a clock cycle, and can also serve as intermediate test points. The chosen image quality metrics can be generated after each stage in order to validate a small number of algorithm modifications at a time. In addition to the testing of the fundamental operations, the high-level modeling languages lend well to the generation of test vectors that are necessary to validate any C and HDL code. After laying out the pipeline stages, the design is prototyped using an HDL such as Verilog or VHDL. Again, the results generated from the HDL, whether from a test bench or emulation, can be verified using the same high-level programming language as before.

#### 4.2 Design for Implementation Guidelines

As presented in Chapter 3 and validated by the results in Chapter 6, during the design for implementation process of the GSEG algorithm, it was discovered that a number of changes made to the original algorithm resulted in a more efficient implementation. These were compiled into a set of guidelines that, when coupled with the design flow, form the DFI methodology.

At the present time, the DFI guidelines are:

• Selecting an appropriate image quality metric and defining a tolerable amount of degradation.

The tolerance for error in the overall result of the algorithm is a valuable parameter as it will be used to validate all modifications made to the original algorithm. Once it has been defined, it serves as the basis for evaluating the results of the remaining guidelines. This prevents striving for functional correctness at a higher precision than is required by an application, a practice which should be avoided as much as possible.

• Using minimal operand representation ranges.

In high-level models of algorithms, standard operand sizes are often used. This is perfectly acceptable for achieving functional correctness, but implementing a 64-bit floating-point number is very costly, especially if only eight to sixteen bits are required. Selecting efficient representation ranges for operands is an easy way to reduce resource utilization and congestion during implementation.

• Using scale factors to represent fractional numbers as fixed-point integers.

o Subsequently, using integer arithmetic units whenever possible.

The use of floating-point numbers also requires the use of floating-point arithmetic units. This can be avoided by using large constant multipliers as scale factors. By scaling fractional numbers up to integers, any required amount of precision can be preserved. This allows for the use of standard integer arithmetic units, which require fewer resources than floating-point units.

• Rounding constant multipliers/divisors to powers of two.

When the second operand of a multiplication or division is a constant that can be reasonably rounded to a power of two, the operation can be effectively eliminated. The determination of "reasonably" is left to the expertise of the algorithm developer and his definition of tolerable degradation. If this method of rounding is not acceptable, round constants to the nearest integer and try to apply the next guideline.

• Avoiding division at all costs.

As was mentioned in the previous chapter, division can be performed in a variety of ways, any of which are costly. In the cases where the divisor is a constant, division can always be replaced by multiplication. The constant can be inverted, and if a fractional portion remains, another scale factor can be applied to facilitate integer multiplication. For cases where the divisor is not a constant and no simplifications exist, then action should be taken to use a division algorithm that is most efficient for the application. This may require weighing a tradeoff between execution time and resource utilization.

#### • Using pre-existing IP cores whenever possible.

Chances are that most of the operations required by an algorithm have already been implemented as IP cores or even custom cores. Having a working knowledge of the cores available to the hardware designer should influence the operations chosen by the algorithm developer when the DFI methodology is applied.

• Accepting an approximate operation.

For cases where no pre-existing cores are applicable, an approximate operation may be required (e.g., approximation of the cube root presented in Chapter 3). Consider suitable replacement operations and evaluate their effects based on metrics or subjective evaluation of the resulting image. A custom core or adaptation of an existing core may ultimately be necessary if the approximation is not tolerable.

• *Applying the DFI process iteratively.*

With a tolerable level of image degradation already defined, multiple iterations of the DFI process can be performed until a maximally efficient design is achieved. As G. Karakonstantis et al. noted in [8], different portions of a given algorithm can contribute different amounts to overall image quality. Numerous combinations of different modifications could result in reaching the threshold of image quality; however, some may be more efficient than others in terms of standard implementation parameters. That is, the tolerable level of image degradation may be reached solely by maximally reducing the representation range of the operands and data buses. On the other hand, the same level of image degradation could be achieved by balancing a reduction in representation range and also an approximation of an operation. These tradeoffs should be considered by the designer in order to achieve a truly efficient algorithm implementation for their given application.

#### 4.3 General Applicability of the Proposed Methodology

The major benefit of the DFI methodology is that it is ultimately flexible in nature. As algorithm developers likely have their own design process based upon experience, it was imperative to propose a design methodology that could be used as an addendum to their current processes. This allows the methodology to be applied to algorithms that have already been designed, as well as algorithms that are currently in development. Once a developer has been introduced to the concepts of designing for implementation, it is likely that many of the guidelines will be taken into account as supplemental procedures during their own design process.

An additional benefit of the methodology is that it is inherently an iterative process, meaning that multiple iterations of its application to an algorithm will eventually converge to an optimal solution. This concept, however, also presents a potential pitfall. As has been mentioned previously in this work, different aspects of an image processing algorithm can contribute differently to overall image quality [8], but also impact other design parameters. Elaborating further, an inexperienced developer could spend the majority of their time attempting to optimize a portion of the algorithm that won't result in a noticeable reduction in execution time, logic utilization, or power consumption. For this reason, a method of analyzing the savings attributed to the different guidelines presented in the previous section would be useful. This could be done with a type of cost-table solution for different transforms and guidelines, but such an addition would be done as future research and would require the application of this methodology on a variety of image processing algorithms.

The flexibility of this methodology provides potential for it to be applied in other areas of digital implementation. Although the proposed methodology was designed with image processing algorithms in mind, a majority of the concepts presented in the guidelines are applicable to any type of digital processing algorithm that needs to be implemented in hardware, such as any DSP algorithms. Before it could be applied to other fields, however, a tolerance for error would need to be defined specific to the application desired. That is, a parameter that is analogous to image quality in this work would need to be identified.

# Chapter 5: Implementation of the Test Vehicle

In the previous two chapters, an example of designing an algorithm for implementation and a design for implementation methodology were shown. The DFI methodology can transform high-level MATLAB code into synthesizable HDL code, according to the design flow presented in Chapter 4. In this chapter, the overall process of implementing the various modules from MATLAB code is described in detail. More specifically, the conversions between different programming languages and programming levels are discussed.

#### 5.1 Conversions between Programming Languages

As was introduced earlier in this work, algorithms are often developed using highlevel modeling languages such as MALAB or MAPLE. While these languages are well suited for fine-tuning parameters and quickly testing an algorithm, they do not discretely call out hardware resources. For this reason, the first step leading to synthesizable HDL is to dissect the algorithm within the high-level modeling language. By dissecting the algorithm, the fundamental operations can be identified and used to replace any intrinsic functions that have been called. This is a crucial step for targeting hardware and for even writing C-code, as MATLAB functions (for an example) do not always directly translate to functions in C. Converting the high-level model of the algorithm into a low-level model, using the same programming language, is a relatively quick way to verify that the fundamental operations and representation ranges identified were correct. Once the low-level model is written in terms basic operations or functions for which the details are known, a C-code version can be written. In principal, a C-code model could be written directly from the high-level model of the algorithm, however it would not be as easy to verify the operations. Regardless of whether or not a low-level model is created as an intermediate step, the conversion from a high-level modeling language to C-code presents a number of difficulties. Using MATLAB as an example language for a starting point, the complications experienced from a conversion to C-code are presented here.

The first problem encountered was the ability for an intrinsic function to have other intrinsic functions called as the input. The nesting of multiple functions as the input of a function presents two kinds of challenges. One challenge is that this piece of code is much longer and more complex than it seems at first glance. The dissection of one of these lines of code, depending upon the level of nesting involved, can take considerably longer than expected resulting in poor estimations of overall development time requirements. A second challenge arising from this coding style is that the code becomes much more difficult to navigate and step through in the debugger. One must take careful consideration to track which function they are actually stepping through. The representation ranges and variable types being used may change throughout these nested functions and must also be taken into consideration.

This leads directly into the next difficulty experienced with such a conversion between languages. Most MATLAB functions have multiple options for a given operation based on the input type, since the input types aren't known until execution time. Additionally, input parameters can be added to certain intrinsic functions or defaults will be used if none are specified. These make a conversion to C-code more difficult, as some functions may change based upon input type. One example of this is the basic histogram function. Without going into great detail, one can see that the creation of an 8-bit histogram is slightly different than that of a 16-bit histogram. Again, this would likely not be considered when writing the high-level model in MATLAB, however, when writing a Ccode model these details need to be known.

Other complications are the special operators that are intrinsic within MATLAB. Operators such as [ ], ', and (:) are specifically matrix declarations and matrix math operations. The [] operator is used to declare arrays and matrices in-line, and the (:) operator is used to denote an entire row of an array. The special operator ' denotes a matrix transposition, which would require a number of for-loops to implement in C-code. Additionally, the matrix mathematic versions of multiplication and division require multiple for-loops to implement. There are number of other special operators that do not map directly to a C function, adding complexity to the conversion between languages.

As mentioned earlier in this section, the input types are not known to the function until execution. To add to this complication, the sizes are not known either. Take the following lines of MATLAB code as an example:

%%Sample MATLAB Code:

A = [1 2 3; 4 5 6; 7 8 9;]; B = [5 5 5; 5 5 5; 5 5 5;]; C = A(A>B) D = A>B

The results from the sample code are as follows:

| C = | 7 |   |   |

|-----|---|---|---|

|     | 8 |   |   |

|     | б |   |   |

|     | 9 |   |   |

|     |   |   |   |

| D = | 0 | 0 | 0 |

|     | 0 | 0 | 1 |

|     | 1 | 1 | 1 |

In this simple example code, two three-by-three matrices were defined. In the third line, C is calculated at run-time to be a four-by-one column vector of type double. Note that only two special operators were used in the line where C was calculated and that the inputs A and B were both of type *double*. In the fourth line of the sample code, D is calculated using only one special operator and the result is a three-by-three matrix of type *logical*. This sample code shows how simple nuances between two lines of code can change both the size and type of results, based on the indexing involved for calculating C. When converting to C-code, the designer needs to take into account the variable types and sizes that are the result of a function execution.

The final hurdle when converting from MATLAB to C-code is one that cannot be jumped, figuratively speaking. Certain intrinsic MATLAB functions are considered proprietary and are therefore off-limits to the casual user. Within the code of the function, these are known as MTALAB executables (MEX-files) and will take the place of the function details that one may be trying to discover or step-into with the debugger. Since these functions don't give the user any insight as to what calculations are taking place, the only way around them is to research similar functions. Once a number of possible functions are found from literature, they can be modeled in MATLAB and the results can be compared. In some cases, the algorithms found during this research may have results that match MATLAB's results exactly. Other times, an approximation can be found and the results have to be deemed acceptable for the application in order to move forward.

In fact, for almost all algorithm steps presented in Chapter 3, the results were reproduced exactly with the low-level model (without modifications). For the conversion from sRGB to linear sRGB, an approximate function is being used. The color space conversion function implemented by MATLAB uses curve-fitting procedures that were deemed inefficient for the hardware implementation in this work. A review of literature regarding color space conversions found an alternative piecewise function for the operation, which was shown in Chapter 3. The results produced by the low-level model of the alternative function were deemed to be acceptable for the application when compared to the intrinsic MATLAB function's results.

#### 5.2 Image Quality Metrics and Validation

Since the original GSEG algorithm is written using MATLAB, it is natural to use MATLAB to create the low-level model of the GSEG algorithm and therefore to validate its results. The first step in applying the DFI methodology, as was presented in Chapter 4, is to identify a metric, or a number of metrics, to be used for evaluating algorithm modifications. In order to validate the algorithm modifications made in Chapter 3, Section

1, test images and image quality metrics are selected. The same images database used for evaluating the GSEG algorithm [15] is selected to evaluate the DFI methodology. By using this database, any degradation or effects on the overall segmentation maps can be assessed by comparison with original GSEG results.

Next, the image quality metrics are selected. Those chosen include: the 2dimensional correlation coefficient [16] (CORR2), the peak signal-to-noise ratio [17] (PSNR), and the structural similarity index [18] (SSIM). Each of the metrics selected can only compare two two-dimensional image planes, which are represented by variables f and g in the equations presented in this section. Thus, if an RGB image is being compared to a known good image, three CORR2 results would be calculated, one for each red, green, and blue plane.

The 2D correlation coefficient is selected for its ease of use, as it is an intrinsic MATLAB function. Another advantage is that it produces a single result, between zero and one, as opposed to a matrix of results for the image plane being validated. The CORR2 function shows the linear dependence, or lack thereof, between the two planes by way of Equation 5.1, and the result is denoted by r.

$$r(f,g) = \frac{\sum_{m} \sum_{n} (f_{m,n} - \bar{f}) (g_{m,n} - \bar{g})}{\sqrt{\left(\sum_{m} \sum_{n} (f_{m,n} - \bar{f})^{2}\right) \left(\sum_{m} \sum_{n} (g_{m,n} - \bar{g})^{2}\right)}}$$

(5.1)

The next two image quality metrics are chosen based on a literature review of industry standard methods for comparing the likeness of two images, the first of which is the Peak Signal to Noise Ratio. Calculating the PSNR is a two part process, beginning with the Mean Squared Error (MSE) in Equation 5.2a. The PSNR is then calculated in decibels using the MSE and the total number of bits used to represent a pixel's value, denoted as b in Equation 5.2b.

$$MSE(f,g) = \frac{\sum_{m} \sum_{n} (f_{m,n} - g_{m,n})^{2}}{mn}$$

(5.2a)

$$PSNR = \log_{10} \frac{(2^b - 1)^2}{MSE} dB$$

(5.2b)

The structural similarity index (SSIM) is the final metric selected to evaluate the modifications made to the GSEG algorithm. The SSIM method is chosen in addition to the PSNR method, since it has been shown that specific cases of image degradation are not reflected by the PSNR [18]. Namely, when the MSE is equal to zero the PSNR does not reflect the difference in image quality. Although the SSIM equations are not presented here in detail, they can be found in their original publication [18]. The authors also provided a MATLAB function for calculating the SSIM index, which is used in this work [19].

Since one of the image quality metrics is an intrinsic MATLAB function and another is provided in MATLAB from [19], it is again natural to validate the modifications using MATLAB. To reduce the overhead of testing for future images, a number of MATLAB scripts were written to automate the process. The loading of known good images, reorganization of pixels, scaling, and displaying of results are just some of the functions handled by the scripts. These scripts are used to evaluate the images at every step throughout the DFI design flow such as low-level MATLAB code results, C-code results from the host PC, Verilog test bench results, and MCF emulation results. The repetitive use of the scripts ensured that there were no discrepancies or user errors between tests.

#### 5.3 Test Setup