# **Rochester Institute of Technology**

# **RIT Digital Institutional Repository**

Theses

8-2005

# Analytical and numerical modeling, fabrication and RF measurement techniques for RF planar micro-inductors on silicon

Daniel W. Brown

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Brown, Daniel W., "Analytical and numerical modeling, fabrication and RF measurement techniques for RF planar micro-inductors on silicon" (2005). Thesis. Rochester Institute of Technology. Accessed from

This Thesis is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

# Analytical and Numerical Modeling, Fabrication and RF Measurement Techniques for RF Planar Micro-Inductors on Silicon

by

#### Daniel W. Brown

A Thesis submitted in Partial Fulfillment of the

Requirements for the Degree of

MASTERS OF SCIENCE

in

**Electrical Engineering**

| Approved by: | Professor | Jayanti Venkataraman                     |  |  |  |  |

|--------------|-----------|------------------------------------------|--|--|--|--|

| 11 ,         |           | (Dr. Jayanti Venkataraman -Advisor)      |  |  |  |  |

|              | Professor | Santosh K. Kurinec                       |  |  |  |  |

|              |           | (Dr. Santosh Kurinec – Committee Member) |  |  |  |  |

|              | Professor | Syed Islam                               |  |  |  |  |

|              |           | (Dr. Syed Islam - Committee Member)      |  |  |  |  |

|              | Professor | Robert Bowman                            |  |  |  |  |

|              |           | (Dr. Robert Bowman - Department Head)    |  |  |  |  |

DEPARTMENT OF ELECTRICAL ENGINEERING

COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NEW YORK

August 2005

# THESIS RELEASE PERMISSION

# DEPARTMENT OF ELECTRICAL ENGINEERING

# **COLLEGE OF ENGINEERING**

# ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NY

# **Title of Thesis:**

Analytical and Numerical Modeling, Fabrication and RF Measurement Techniques for RF Planar Micro-Inductors on Silicon

| I,  | Daniel  | W.   | Brow    | 'n,  | hereby    | grant | ŗ  | permission   | to   | Wallace | N  | <b>1</b> emoria | al . | Lib | rary  | of | the |

|-----|---------|------|---------|------|-----------|-------|----|--------------|------|---------|----|-----------------|------|-----|-------|----|-----|

|     |         |      |         |      |           |       |    | reproduce    |      |         | in | whole           | or   | in  | part. |    | Any |

| rep | roducti | on v | vill no | t be | e for con | nmerc | ia | l use or pro | fit. |         |    |                 |      |     |       |    |     |

| Signature Daniel W. Brown | Date | 8-30-05 |

|---------------------------|------|---------|

|---------------------------|------|---------|

### **ACKNOWLEDGMENTS**

I would like to thank Dr. Venkataraman for her guidance and instruction. Her passion for electromagnetics, education, and research is impressive and admirable. It has been a joy to work with someone I truly look up to.

I would also like to thank Dr. Kurinec for supporting my work. Her dedication to the institute and to research is evident and invaluable. My gratitude is also due to Dr. Islam, who graciously reviewed my thesis.

I must thank everyone involved with the fabrication process including:

Cody Washburn, Jay Cabacungan, Dan Jaeger, and Gary Fino. The success of this project was a direct result of your hard work. The staff of the SMFL deserves a great deal of recognition for their willingness to assist me even at their busiest times.

To my lab partners Marie Yvanoff and William Lambert, I thank you for all of our discussions academic or not. I can only hope my future endeavors surround me with people as kind and intelligent as the both of you. Good luck always.

Mom and Dad, thank you for your support throughout the past seven years. I am very lucky to have you as parents.

Amanda, you are my greatest inspiration and best friend. Thank you for supporting me.

This work was supported by the National Science Foundation under grant ECS 0219379.

## **ABSTRACT**

In mixed signal integrated circuits, the role of passives has become increasingly important. In particular, the characterization and implementation of an embedded planar coil inductor presents several challenges. The present work is a comprehensive study of micro inductors that includes analytical modeling, numerical simulation, in-house fabrication processes, circuit implementation in silicon, and RF measurement techniques.

Although the inductor is widely integrated on silicon, there is still a need for closed form expressions for inductance and the quality factor. In addition, amongst the numerous commercially available simulation packages, there still is a need to identify the tool that best suits the design and implementation of micro-inductors on silicon. In this work, an analytical model is presented based on a desegmentation technique, which removes segments from a rectangular cavity to create the inductor coil geometry. Defining the Green's function for each segment, the boundary conditions are applied to obtain a closed form expression for the Z matrix from which the inductance and Q have been obtained. For a numerical modeling, Ansoft's High Frequency Structure Simulator (HFSS) is chosen as the preferred tool for an accurate and frequency dependent analysis. Several inductor geometries have been modeled analytically and have been validated with HFSS where in each case there is excellent agreement. The model has also been successfully applied to irregularly shaped power planes that commonly occur in mixed signal circuits.

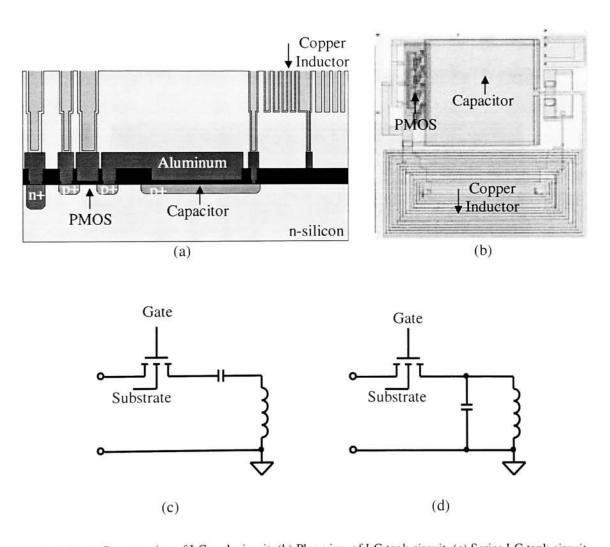

The present work has established a fabrication process for micro-inductors using technologies available in the Semiconductor and Microsystems Fabrication Laboratory

(SMFL) at RIT. A fabrication process has been developed to integrate inductors, transformers, capacitors, and PMOS (P-type Metal Oxide Semiconductor) transistors. Inductors and transformers have been made from copper and imbedded in a thick PECVD SiO<sub>2</sub> film. The process allows for an optional aluminum ground plane under the copper structures. Capacitors have been formed using the gate oxide as a dielectric and heavily doped silicon and aluminum as the electrodes. PMOS transistors have been implemented to control two varieties of LC tank circuits (parallel and series).

The final contribution of the present work is establishing RF test methods for measuring inductance, and calculating the quality factor (Q). Experimental RF testing is performed using high frequency Cascade Microtech ground-signal-ground (GSG) probes and the 9100 probe station. Data has been captured using an Agilent 8363B network analyzer with a frequency range from 10 MHz to 40 GHz. A calibration procedure has been developed for a full two port measurement and a methodology has been optimized for measuring the impedance [Z] matrix and the scattering [S] matrix. The input impedance is extracted from the [Z] matrix and Q has been calculated. There is excellent agreement between experimental results, numerical results from HFSS, and analytical results from the desegmentation technique.

# **TABLE OF CONTENTS**

| ACKNOWLEDGMENTS                                                     | ii  |

|---------------------------------------------------------------------|-----|

| ABSTRACT                                                            | iii |

| TABLE OF CONTENTS                                                   | v   |

| LIST OF FIGURES                                                     | ix  |

| 1. Introduction                                                     | 1   |

| 2. Present Work and Motivation                                      | 4   |

| 2.1 Motivation and Purpose                                          | 4   |

| 2.2 Major Contributions                                             | 4   |

| 2.2.1 Analytical Modeling                                           | 4   |

| 2.2.2 Physical Realization and Testing of Micro-fabricated Circuits | 5   |

| 3. Inductor Design and Modeling                                     | 6   |

| 3.1 Analytical Modeling                                             | 7   |

| 3.1.1 Segmentation and Desegmentation                               | 7   |

| 3.2 Mathematical Formulation                                        | 10  |

| 3.2.1 Green's Function for Rectangular Geometries                   | 10  |

| 3.2.2 Single Segment Removal                                        | 13  |

| 3.2.3 Convergence Analysis for Single Segment Removal               | 18  |

| 3.2.4 Two Segment Removal                                           | 23  |

| 3.2.5 Convergence Analysis for Double Segment Removal               | 25  |

| 3.2.6 N Segment Removal                                             | 28  |

| 4. Numerical Modeling                                               | 29  |

|    | 4.1   | Available Numerical Modeling Tools                       | 29 |

|----|-------|----------------------------------------------------------|----|

|    | 4.2   | HFSS                                                     | 29 |

|    |       | 4.2.1 Structure Definition in HFSS                       | 29 |

|    |       | 4.2.2 Port Definition in HFSS                            | 31 |

|    |       | 4.2.3 Analysis Setup in HFSS                             | 32 |

| 5. | Com   | parison of Analytical and Numerical Techniques           | 33 |

|    | 5.1   | Rectangular Ring                                         | 33 |

|    | 5.2   | L- Shaped Plane                                          | 34 |

|    | 5.3   | One Turn Inductor                                        | 36 |

| 6. | Ferri | ite Filled Inductors                                     | 39 |

|    | 6.1   | Predicted Effect of Magnetic Material Filling Using HFSS | 39 |

| 7. | Physi | ical Realization of Microfabricated Circuits             | 42 |

|    | 7.1   | Design Considerations                                    | 42 |

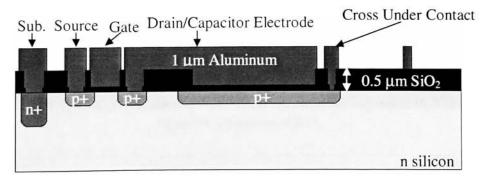

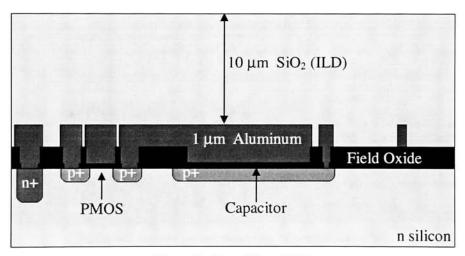

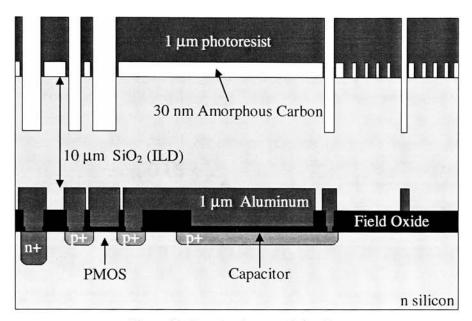

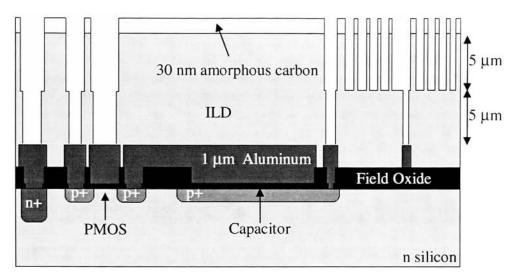

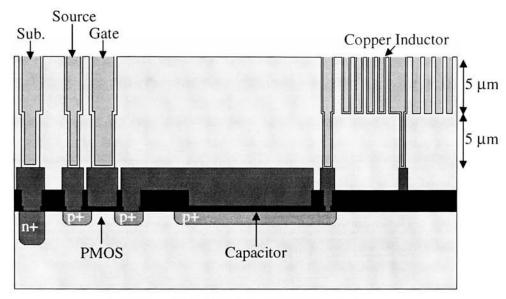

|    | 7.2   | Process Flow                                             | 44 |

|    |       | 7.2.1 Front-End Process                                  | 44 |

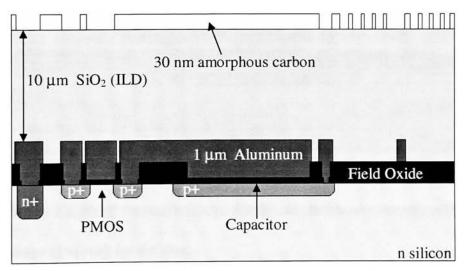

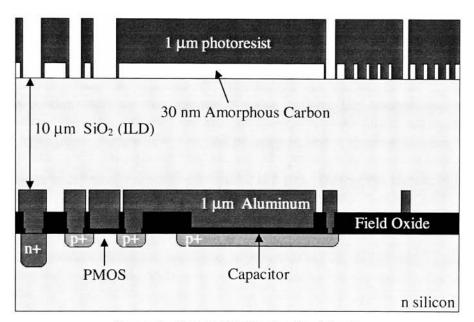

|    |       | 7.2.2 Back-End Process                                   | 47 |

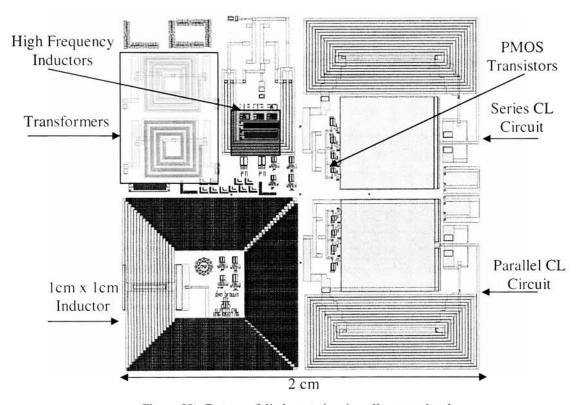

|    | 7.2   | Photomask Layout                                         | 52 |

|    | 7.4   | Ferrite Filling Technology                               | 54 |

| 8. | Expe  | rimental Results                                         | 56 |

|    | 8.1   | Experimental Test Setup                                  | 57 |

|    |       | 8.1.1 RF Testing                                         | 58 |

|    | 8.2   | Comparison of Modeling and Measured Results              | 64 |

|        | 8.2.1 One Turn On-Chip Inductor (Thin Side Segment)               | 64       |

|--------|-------------------------------------------------------------------|----------|

|        | 8.2.2 One Turn On-Chip Inductor (thick side segment)              | 68       |

|        | 8.2.2 Meander Line Inductors                                      | 71       |

|        | 8.2.3 PMOS Transistor and Diode Testing                           | 73       |

| 9. Con | ısion                                                             | 77       |

| 9.     | Summary of Contributions                                          | 77       |

|        | 9.1.1 Analytical and Numerical Modeling                           | 77       |

|        | 9.1.2 Fabrication and Circuit Implementation of On-Chip Micro-Ind | uctors78 |

|        | 9.1.3 Measurement Techniques                                      | 78       |

| 9.     | Future Work                                                       | 79       |

| Public | ions from the Present Work                                        | 80       |

| Appen  | x A                                                               | 81       |

| A      | MATLAB Code for Desegmentation Technique                          | 81       |

|        | A.1.1 Desegmentation.m (main program)                             | 81       |

|        | A.1.2 Zij.m                                                       | 88       |

|        | A.1.3 Ports.m                                                     | 89       |

| Appen  | x B                                                               | 90       |

| В.     | Back-End Process Flow                                             | 90       |

|        | B.1.1 Amorphous Carbon Deposition                                 | 90       |

|        | B.1.2 Patterning of Amorphous Carbon Film                         | 91       |

|        | B.1.3 Patterning of Photoresist for Vias                          | 92       |

|        | B.1.4 Two Level Etch Process                                      | 94       |

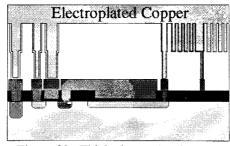

| B.1.5 M    | Netalization and CMP | 95 |

|------------|----------------------|----|

| References |                      | 97 |

# **LIST OF FIGURES**

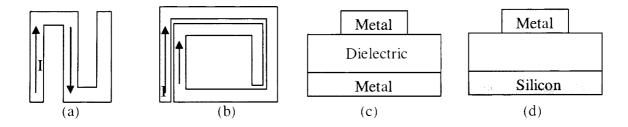

| Figure 1. | (a) Meander line setup. (b) Rectangular spiral setup. (c) Cross section of metal trace over metal ground plane. (d) Cross section of metal trace over silicon6                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

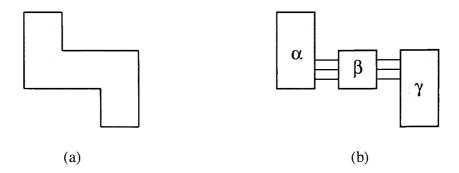

| Figure 2. | (a) Irregular shape for which segmentation can be applied. (b) Regularly shaped segments that constitute irregular shape in Figure 2a8                                                                                                |

| Figure 3. | (a) Irregular shape for which desegmentation can be applied. (b) $\gamma$ segment composed of $\alpha$ and $\beta$ segments. (c) $\beta$ segments being removed to yield irregular shape Figure 2a.                                   |

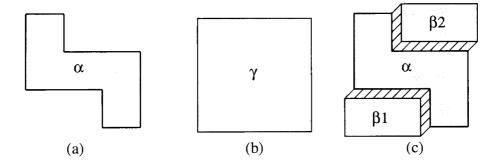

| Figure 4. | (a) Lumped element model of on chip spiral inductor. (b) Z matrix representation                                                                                                                                                      |

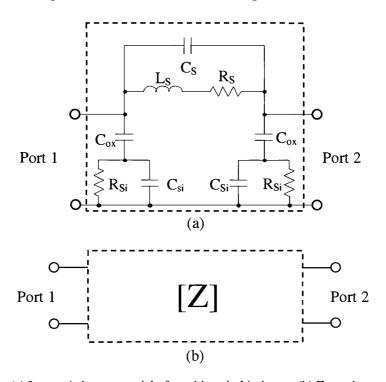

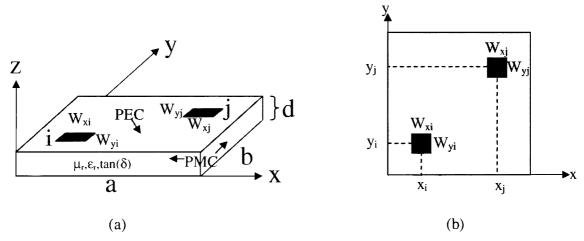

| Figure 5. | (a) Microstrip cavity showing port definitions. (b) Plan view of microstrip cavity showing port definitions                                                                                                                           |

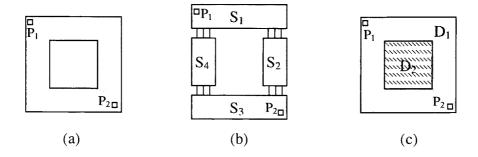

| Figure 6. | (a) Rectangular ring pattern. (b) Application of segmentation. (c) Application of desegmentation                                                                                                                                      |

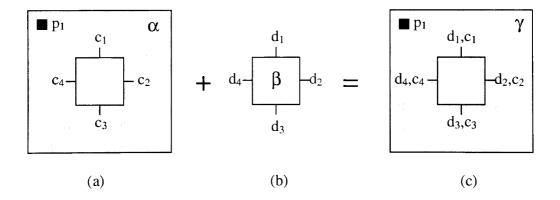

| Figure 7. | Illustration of segmentation when $Z_{pp.}^{\alpha}$ can not be found. (a) $\alpha$ segment. (b) $\beta$ segment. (c) $\gamma$ segment                                                                                                |

| Figure 8. | Desegmentation method applied as expressed in (11)15                                                                                                                                                                                  |

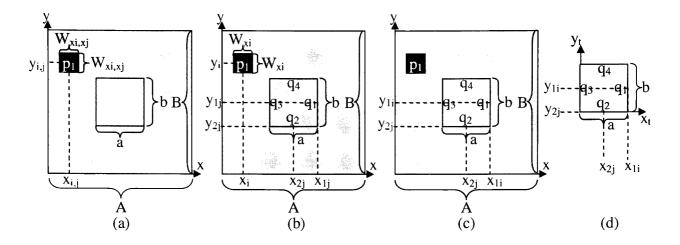

| Figure 9. | (a) Port definition for $Z_{pq}^{\gamma}$ . (b) Port definition for $Z_{pq}^{\gamma}$ . (c) Port definition for $Z_{qq}^{\gamma}$ . (d) Port definition for $Z_{qq}^{\beta}$                                                          |

| Figure 10 | . (a) Pattern tested for convergence. (b) Dimensions and material parameters. 20                                                                                                                                                      |

| Figure 11 | . Eigenmode convergence for S <sub>11</sub> for ring pattern20                                                                                                                                                                        |

| Figure 12 | . (a) Change in first two resonant frequencies $(f_{r1}, f_{r2})$ vs. n and m eigenmodes                                                                                                                                              |

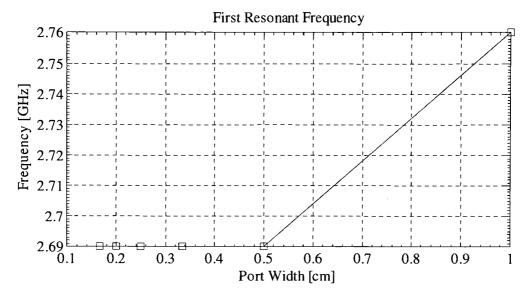

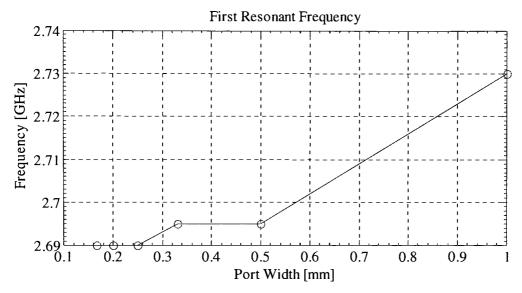

| Figure 13 | . First resonant frequency vs. q port width (m=n=34)                                                                                                                                                                                  |

| Figure 14 | . Second resonant frequency vs. q port width (m=n=34)22                                                                                                                                                                               |

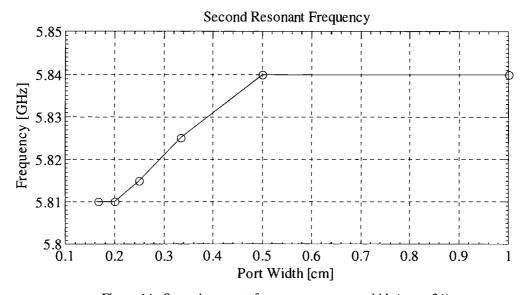

| Figure 15 | . (a) Initial $\gamma$ segment ( $\gamma_1$ ). (b) $\beta_1$ segment. (c) $\alpha_1$ or $\gamma_2$ segment. (d) $\beta_2$ segment. (e) Final $\alpha$ segment $\alpha_2$ . (f) Physical parameters of rectangular ring under analysis |

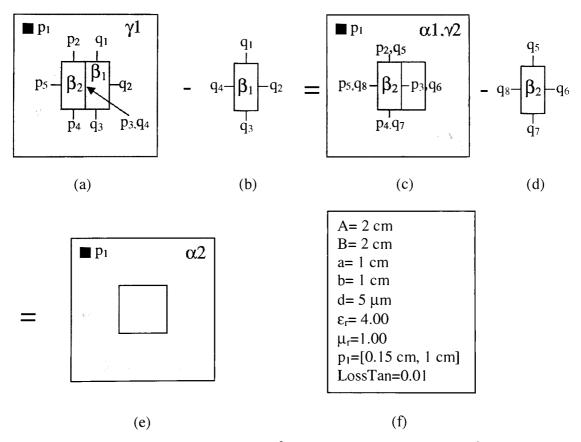

| Figure 16 | Eigenmode convergence for two segment removal for the first two resonant frequencies                                                                                                                                                  |

| Figure 17 | . Convergence for first resonant frequency when two segments are removed (m=n=34)                                                                                                                                                     |

| Figure 18 | Convergence for second resonant frequency when two segments are removed (m=n=34)                                                                                                                                                      |

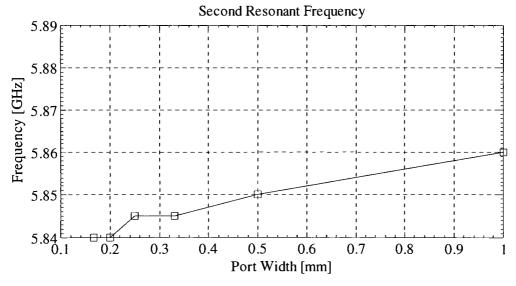

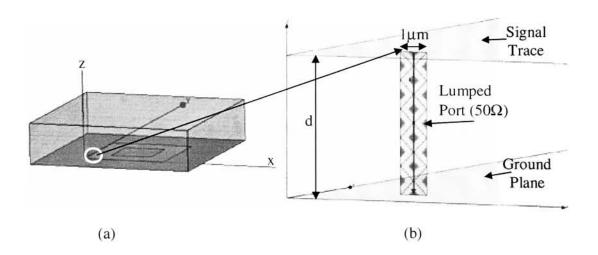

| Figure 19. | (a) Plan view of a rectangular ring. (b) Cross section of rectangular ring30                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 20. | (a) Perfect electric boundary on ring. (b) Perfect electric boundary on bottom face of dielectric. (c) Radiation boundaries on 5 outer faces of vacuum box.30                 |

| Figure 21. | (a) Angle view of rectangular ring. (b) Zoom of port placement                                                                                                                |

| Figure 22. | (a) Planar view of ring pattern. (b) Parameters used for analysis. (c) HFSS capture of ring pattern. (d) S <sub>11</sub> for ring pattern. 33                                 |

| Figure 23. | Table of resulting resonant frequencies for pattern in Figure 22                                                                                                              |

| Figure 24. | (a) Planar view of L-shaped pattern (b) Parameters used for analysis (c) HFSS capture of L shaped pattern (d) S <sub>11</sub> for L-shaped pattern35                          |

| Figure 25. | Table of resulting resonant frequencies for pattern in Figure 2435                                                                                                            |

| Figure 26. | (a) Plan view of a one turn inductor pattern. (b) Parameters used for analysis. (c) HFSS capture of one turn inductor structure pattern. (d) Inductance for one turn inductor |

| Figure 27. | (a) Segmentation vs. desegmentation vs. measured data                                                                                                                         |

| Figure 28. | Table of resulting inductance at 100MHz and SRF from Figure 2638                                                                                                              |

| Figure 29. | (a) Magnetic material positioned above one turn inductor. (b) Magnetic material positioned between the inductor pattern and the ground plane39                                |

| Figure 30. | HFSS results for magnetic material placed above one turn inductor40                                                                                                           |

| Figure 31. | HFSS results for magnetic material placed between one turn inductor and ground plane                                                                                          |

| Figure 32. | Desegmentation results for a magnetic material placed between one turn inductor and ground plane                                                                              |

| Figure 33. | HFSS Results for magnetic material enhancement                                                                                                                                |

| Figure 34. | Desegmentation results for magnetic material enhancement                                                                                                                      |

| Figure 35. | (a) Cross section of LC tank circuit. (b) Plan view of LC tank circuit. (c) Series LC tank circuit (d) Parallel LC tank circuit                                               |

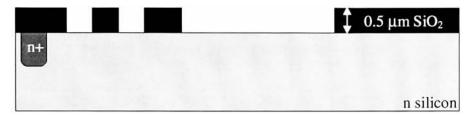

| Figure 36. | Wet thermal oxidation and oxide patterning for n+ diffusion regions44                                                                                                         |

| Figure 37. | n+ spin on dopant and subsequent diffusion44                                                                                                                                  |

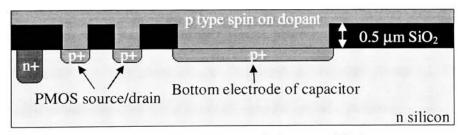

| Figure 38. | Wet thermal oxidation and oxide patterning for p+ diffusion regions45                                                                                                         |

| Figure 39. | p+ spin on dopant and subsequent diffusion                                                                                                                                    |

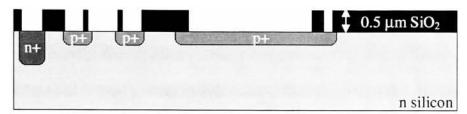

| Figure 40. | Field oxide growth and etch for active regions.                                                                                                                               |

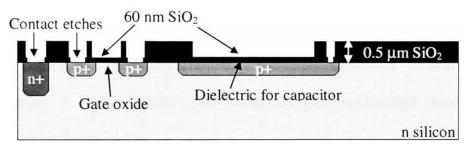

| Figure 41. | Growth of dry thermal gate oxide and subsequent etch for silicon contacts40                                                                                                   |

| Figure 42. | PVD sputter and patterning of aluminum40                                                                                                                                      |

| Figure 43. | Deposition of ILD.                                                                                            | .47        |

|------------|---------------------------------------------------------------------------------------------------------------|------------|

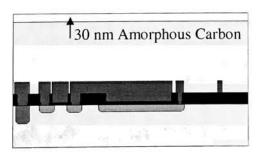

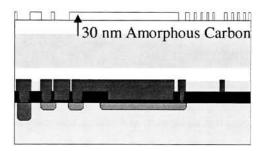

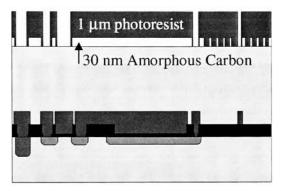

| Figure 44. | Deposition and patterning of amorphous carbon                                                                 | .48        |

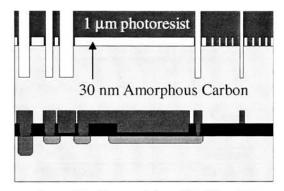

| Figure 45. | Photoresist patterning for via level.                                                                         | .49        |

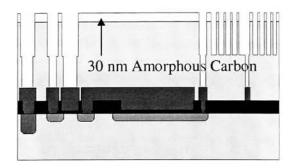

| Figure 46. | 5 μm head start etch for vias.                                                                                | .50        |

| Figure 47. | 5 μm etch of metal 2 trenches.                                                                                | .51        |

| Figure 48. | Cross section schematic after CMP.                                                                            | .52        |

| Figure 49. | Table of critical mask dimensions.                                                                            | .52        |

| Figure 50. | Capture of die layout showing all process levels.                                                             | .53        |

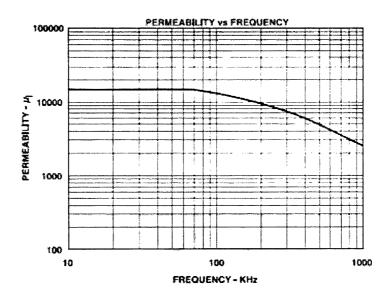

| Figure 51. | Permeability of solid toroids made of V-material from Ferronics []                                            | .54        |

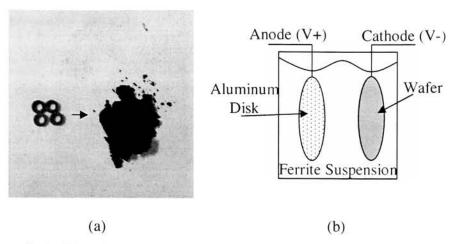

| Figure 52. | (a) Ball milling of toroids resulting in ferrite powder. (b) Depiction of electrophoretic plating of ferrite. | .55        |

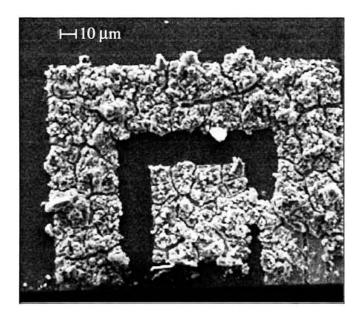

| Figure 53. | Scanning electron micrograph of ferrite coated micro-inductor                                                 | .55        |

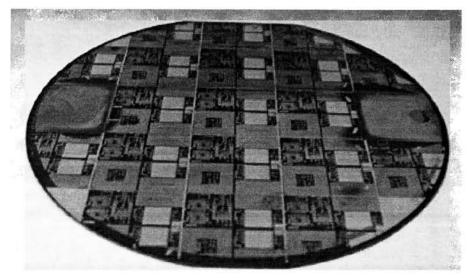

| Figure 54. | Photograph of fabricated 4 inch silicon wafer.                                                                | .56        |

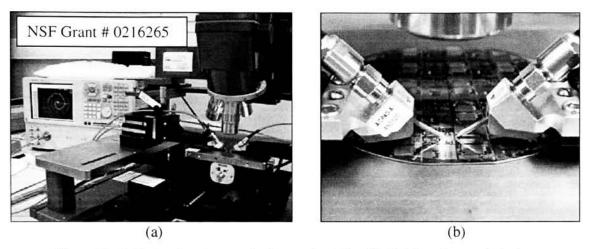

| Figure 55. | (a) Network analyzer and micro-probe station. (b) Probing of copper induct                                    | or.<br>.57 |

| Figure 56. | Photograph showing two port RF probing of inductor using 150 µm pitch GSG probes.                             | .57        |

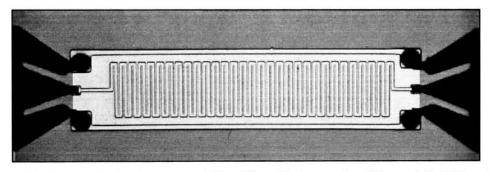

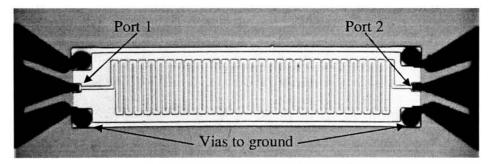

| Figure 57. | Meander line inductor with a layout designed for one port inductance measurements                             | .58        |

| Figure 58. | Two port meander line inductor showing the placement of two ports                                             | .59        |

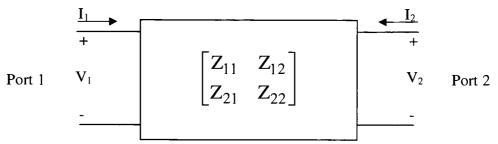

| Figure 59. | Two port network showing input currents and voltages.                                                         | .60        |

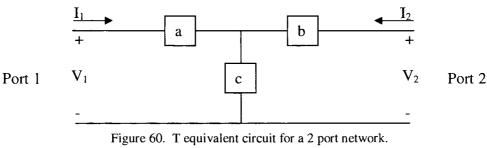

| Figure 60. | T equivalent circuit for a 2 port network.                                                                    | .61        |

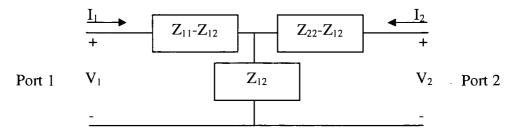

| Figure 61. | T equivalent circuit for a two port reciprocal network                                                        | .62        |

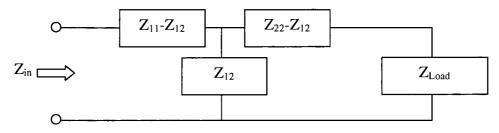

| Figure 62. | Port 2 terminated by load impedance Z <sub>L</sub> .                                                          | .62        |

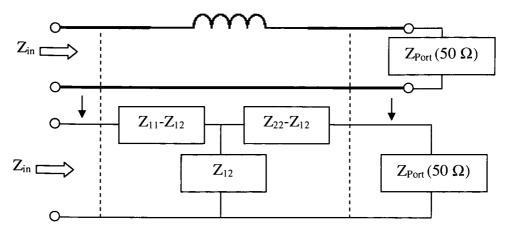

| Figure 63. | Equivalent circuit when two port measurements are performed                                                   | .63        |

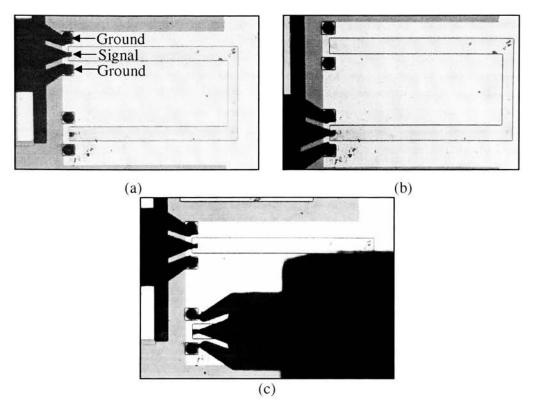

| Figure 64. | Fabricated one turn inductor.                                                                                 | .64        |

| Figure 65. | (a) $Z_{11}$ measurement. (b) $Z_{22}$ measurement. (c) 2 ports measurement for calculating $Z_{12}$          | .65        |

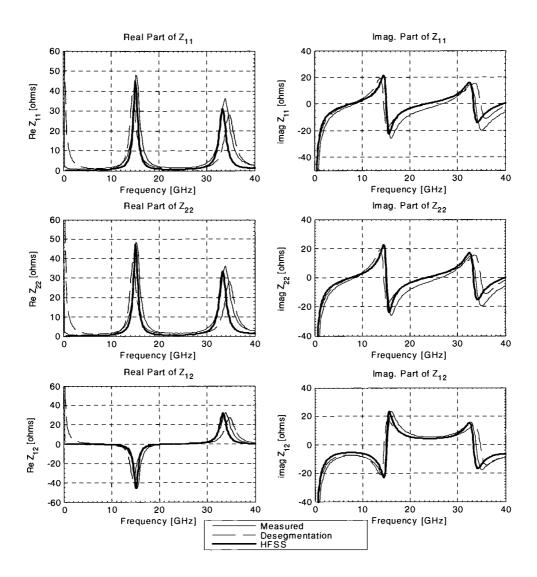

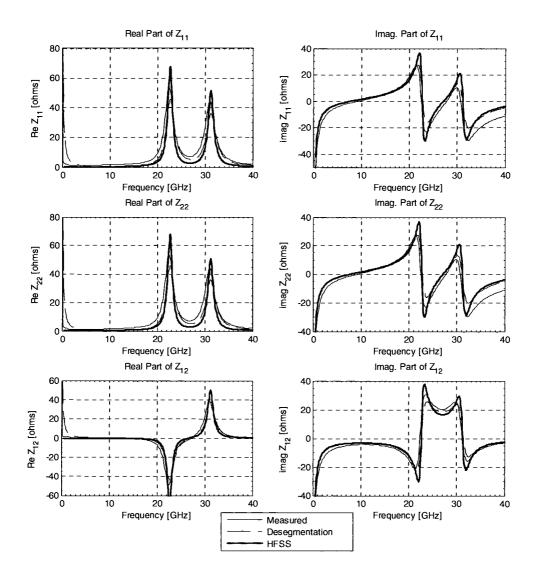

| Figure 66. | Impedance parameters for the one turn microstrip inductor in Figure 64                                        | .66        |

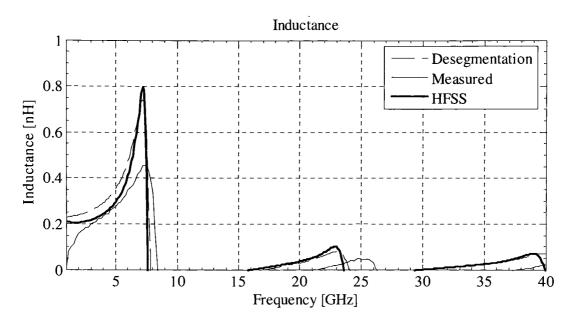

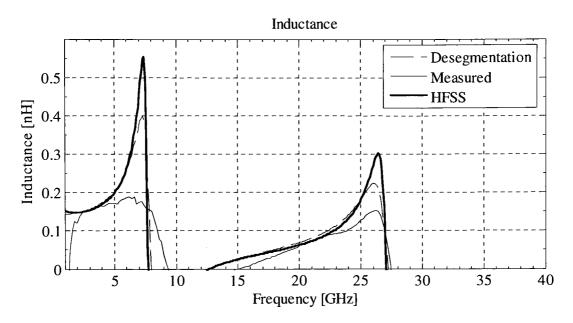

| Figure 67. | Inductance for microstrip inductor in Figure 64.                                                              | .67        |

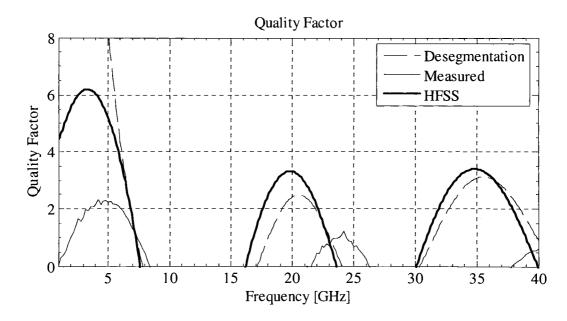

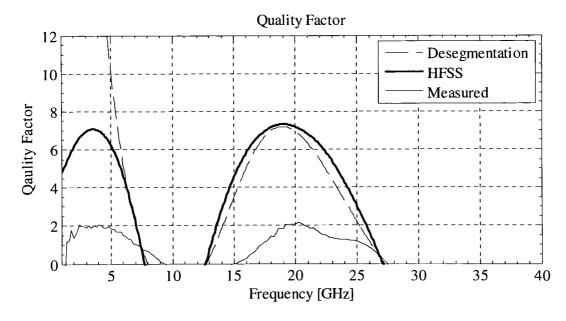

| Figure 68. | Quality factor for microstrip inductor in Figure 64                                                           | .67        |

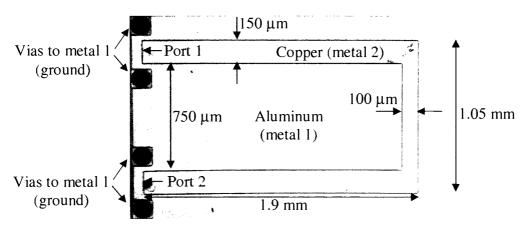

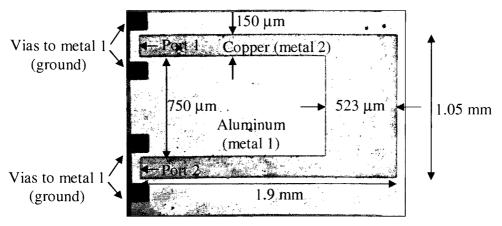

| Figure 69. | Plan view of fabricated one turn inductor                                                                     | .68        |

| Figure 70. | Impedance parameters for the one turn microstrip inductor in Figure 6969                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 71. | Inductance for one turn microstrip inductor in Figure 69                                                                                            |

| Figure 72. | Quality factor Inductance for one turn microstrip inductor in Figure 6979                                                                           |

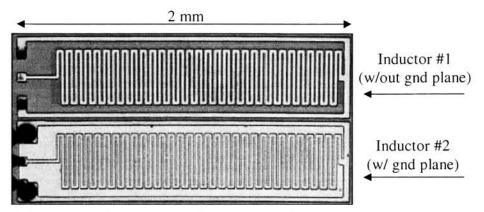

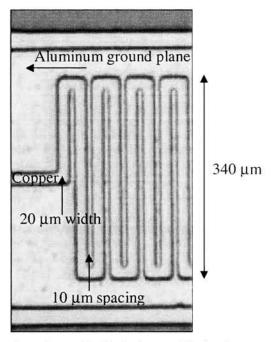

| Figure 73. | Meander line inductors with and without an aluminum ground plane7                                                                                   |

| Figure 74. | Zoomed plan view of meander line inductor with aluminum ground plane7                                                                               |

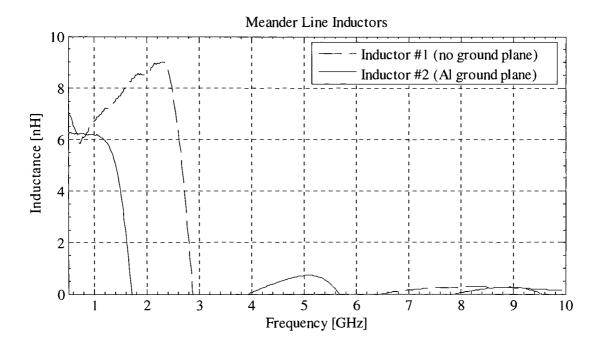

| Figure 75. | One port meander line inductor with and without an aluminum ground plane.                                                                           |

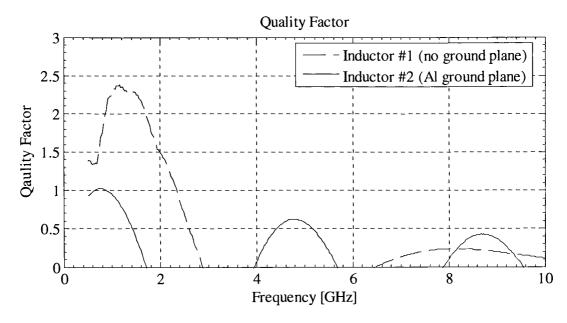

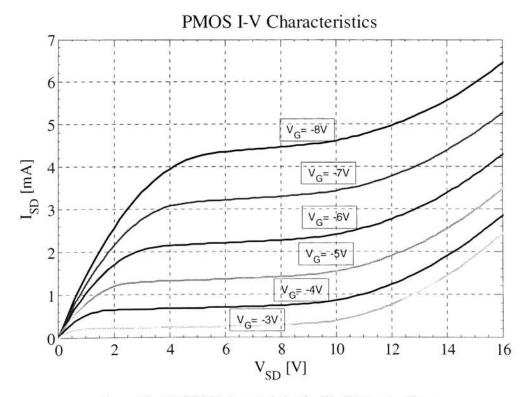

| Figure 76. | Quality factor for two meander line inductors with and without an aluminum ground plane.                                                            |

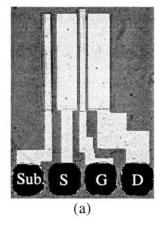

| Figure 77. | (a) Photograph of PMOS transistor showing substrate (Sub), source (S), gate (G), and drain (D) contacts. (b) Circuit symbol for a PMOS transistor74 |

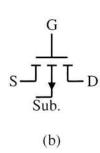

| Figure 78. | PMOS I-V characteristics for W=400 μm, L=10 μm74                                                                                                    |

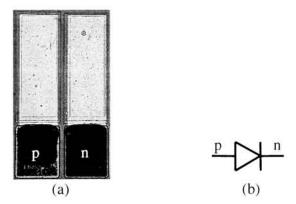

| Figure 79. | (a) Photograph showing fabricated pn diode. (b) Circuit symbol for a diode. 7                                                                       |

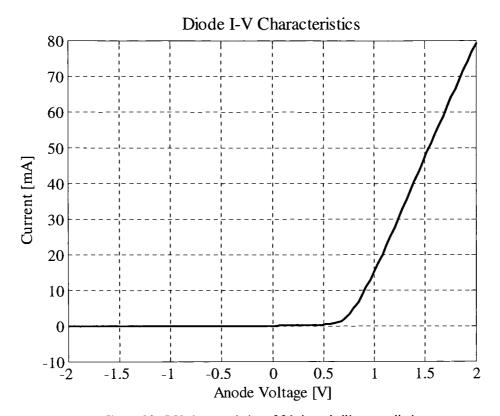

| Figure 80. | I-V characteristics of fabricated silicon pn diode                                                                                                  |

| Figure 81. | Parameters for amorphous carbon deposition in DryTek Quad90                                                                                         |

| Figure 82. | Deposition of amorphous carbon9                                                                                                                     |

| Figure 83. | Specialized lithography details9                                                                                                                    |

| Figure 84. | 30 nm amorphous carbon etch9                                                                                                                        |

|            | Completed etch of amorphous carbon film and strip of resist9                                                                                        |

| Figure 86. | Specialized lithography details9                                                                                                                    |

| Figure 87. | Cross section of via pattern in photoresist and metal 2 in carbon film9                                                                             |

| Figure 88. | 5 $\mu m$ etch into SiO <sub>2</sub> film (ILD).                                                                                                    |

| Figure 89. | Additional 5 µm etch for vias, and 5 µm etch for metal 29                                                                                           |

| Figure 90. | Sputter of tantalum9                                                                                                                                |

| Figure 91. | Sputter of copper9                                                                                                                                  |

| Figure 92. | Thick electroplated copper9                                                                                                                         |

| Figure 93. | Electroplating parameters9                                                                                                                          |

| Figure 94. | Composition of slurry for copper polishing9                                                                                                         |

| Figure 95  | Polished wafer9                                                                                                                                     |

# 1. Introduction

The advancement of integrated circuit (IC) technology has enabled aggressive device scaling leading to the present ability to place hundred of millions of transistors on a single silicon chip. Microprocessors, memory, analog IC's and radio frequency (RF) IC's can all be integrated on a single chip, increasing the functionality of fabricated systems [1]. SoC (system-on-chip) systems combine functions such as digital computing, communications, and other non-CMOS technology. IC RF filters and integrated impedance matching networks are RF circuits that require the incorporation of on chip inductors.

On chip passives such as inductors are of interest in this study. Typically, inductors fabricated on silicon suffer from low self resonant frequencies (SRF), as well as low quality factor (Q factor) [2],[3],[4],[5],[6],[7],[8],[9],[10]. A number of attempts have been made to improve both the SRF and Q factor [2]-[10].

A limitation of fabricating inductors on silicon substrate is the fact that silicon is semi-conductive. This introduces an inherent capacitance that ultimately reduces the SRF. As the inductor moves further form the surface of the substrate, the SRF will increase [8],[11]. It has been proposed that the substrate be removed either by backside [12], or frontside bulk silicon etching [8]. The bulk etching of the silicon substrate removes the associated parasitic capacitance, however, decreases the mechanical stability of the substrate itself. Instead of physically removing the silicon substrate, the anodization of the substrate to form a thick porous silicon film can effectively move the

conductive substrate surface away from the inductor and reduce the parasitic capacitance presented [13],[14], while preserving a greater degree of mechanical stability.

The losses presented by the resistive silicon substrate help to decrease the Q factor [15]. The reduction of resistive losses to the bulk silicon can be accomplished by inserting a solid ground shield made of a highly conductive material. However, a solid ground shield will produce image currents and a negative mutual inductance [3] thereby lowering overall inductance. The insertion of a patterned ground shield has been shown to increase the quality factor of fabricated inductors while limiting image currents that can lower the inductance [3]. However, the use of any conductive ground shield presents a capacitance which lowers the SRF.

The incorporation of ferromagnetic materials has also been proposed to increase both the inductance and quality factor of on chip inductors [16],[17]. By increasing the permeability of the medium that the inductor is immersed, the inductance can be directly affected. The optimal placement of the magnetic material is also of interest and needs to be addressed for inductors with a ground plane.

It is important to consider both cost of integration as well as performance when choosing an improvement method proposed in [3], [16], [6], [10]. Both theoretical modeling and experimental research is required to determine the value of the gains provided by a modified processing scheme. Reduced footprint area, high Q, high SRF, and high EM isolation are all desirable traits for an inductor, but it can be difficult to maximize all simultaneously.

Inductor modeling using a lumped element approach has been extensively reported [5], and [9] and compared with experimental results. Lumped element models have been applied to standard planar spiral inductors [5],[9], as well as multilayer planar spiral inductors [10]. Layout optimization has also been considered [4], where the width of the coil segments varies for a particular coil. By using analytical models, time intensive electromagnetic (EM) full wave solvers can be avoided. The time required for setup and simulation is a disadvantage of numerical full wave solvers. Time intense EM simulations are not practical to implement in mixed signal design. EM full wave solvers are also difficult to integrate into the design process. Analytical methods can also provide a better design methodology and fundamental understanding than numerical tools.

A fabrication process has been to be developed to experimentally test and verify the results obtained through analytical and numerical techniques. In this study, inductors are fabricated with and with out a ground plane. A frequency dependent analytical model has been developed and extended to address circuit patterns such as rectangular inductors above a solid ground plane or shield. Ferrite powder is available, and attempts are being made to characterize the magnetic properties of this material. Attempts are also being made to electroplate the ferrite material between the fabricated inductors and the aluminum ground plane or the inductors and the silicon surface. Modeling has been performed to predict the impedance response when a magnetic medium is inserted in the cavity or placed above the inductor coil pattern.

#### 2. Present Work and Motivation

#### 2.1 Motivation and Purpose

In order to efficiently and accurately model the impedance of on chip passives, an analytical model has been developed. The model presented in this work is tailored to determine the impedance of microstrip geometries that are realized using standard microelectronic processing techniques. The analytical model can provide impedance data over a range of frequencies and incorporates the effect of higher order modes. The effect of permittivity and permeability are also included to account for a variety of materials.

## 2.2 Major Contributions

#### 2.2.1 Analytical Modeling

The analytical model of desegmentation has been modified and extended to enable the removal of multiple segments. Previously, one segment removal has been investigated [21],[22]. The extension of the technique to multiple segments provides the ability to analyze a wider variety of irregular circuit patterns. The results that can be obtained by the technique consist of the scattering [S] and impedance [Z] matrices over a range of frequencies. The Z matrix is used to determine properties such as inductance, quality factor, and self-resonant frequency. Irregularly shaped power planes and rectangular coils are among the geometries investigated. The results generated by the modeling technique presented in this work have been compared to the widely used

electromagnetic full wave solver HFSS. The validation of the desegmentation technique presented allows for circumvention of numerical solvers for future analysis.

## 2.2.2 Physical Realization and Testing of Micro-fabricated Circuits

The verification of the technique presented has been done in part through the physical realization and testing of micro-fabricated inductor geometries. A fabrication process has been fully developed that yielded microstrip circuit patterns alongside MOS transistors, transformers, inductors, and capacitors. A thick (>10μm) inter-level dielectric (ILD) has been patterned with conventional microlithography and etching to produce vias (10μm), as well as trenches (5μm) for copper interconnect. A copper dual-damascene [18] process has been developed to maximize signal trace conductance thereby limiting the loss contributed by the conductor. The incorporation of magnetic materials using electrophoresis (EP) techniques have been investigated both experimentally and theoretically.

A test procedure has been developed and demonstrated for performing on chip measurements and extracting the impedance characteristics of fabricated passives. A network analyzer is used to extract the frequency dependent impedance of the passives under testing. One port and two port measurements have been collected for inductor patterns and each provided inductance values as well as quality factors.

The design, layout, fabrication, testing, simulation, and analytical modeling of on chip inductors have been performed. All aspects have been achieved using technologies available at the Rochester Institute of Technology (RIT).

# 3. Inductor Design and Modeling

The modeling of microstrip geometries can be performed using a variety of software such as Ansoft HFSS, Designer, and Maxwell 3D. Analytical methods exist for inductor patterns typically consisting of lumped element models or distributed circuit models.

When an integrated inductor is considered, a number of configurations can be used. The direction of the windings can be used to either enhance or reduce overall inductance.

Figure 1. (a) Meander line setup. (b) Rectangular spiral setup. (c) Cross section of metal trace over metal ground plane. (d) Cross section of metal trace over silicon.

Figure 1 (a) shows a layout for promoting negative mutual coupling while Figure 1(b) shows a layout for enhancing positive mutual coupling [19].

The presence of a conductive ground plane greatly affects the electrical response of the inductor. The removal of any effective conductive ground plane is difficult because the silicon substrate is conductive and presents a capacitance associated with the inductor. A well-defined ground plane can be achieved by heavily-doping the silicon or patterning a metallic layer under the dielectric as shown in Figure 1(c). If a ground plane is desired, it should be constructed of metal for maximum conductivity to minimize

conductive losses. Microstrip geometries are of interest in this study and have been implemented using conventional microelectronic fabrication techniques.

## 3.1 Analytical Modeling

The primary focus for the analytical modeling in this study involves microstrip geometries where a signal trace is routed above a ground plane. For simple rectangular and circular shapes, a Green's function can be directly found. For irregular shapes where a Green's function is not available, the technique of segmentation or desegmentation can be applied. Segmentation and desegmentation provide a means of determining the frequency dependent impedance response for irregularly shaped patterns. To apply segmentation or desegmentation to irregularly shaped patterns, the irregular pattern must consist of the addition or subtraction (segmentation or desegmentation, respectively) of regular shapes for which a Green's function is available.

#### 3.1.1 Segmentation and Desegmentation

The segmentation and desegmentation methods investigated here use the cavity model to determine the impedance parameters between defined ports on a geometry for which a Green's function exists. Segmentation provides the resulting impedance characteristics for an irregularly shaped structure by adding the effects of regularly shaped geometries [20].

Figure 2. (a) Irregular shape for which segmentation can be applied. (b) Regularly shaped segments that constitute irregular shape in Figure 2a.

Desegmentation can also be applied to the irregular geometry seen in Figure 2(a) as shown in Figure 3.

Figure 3. (a) Irregular shape for which desegmentation can be applied. (b)  $\gamma$  segment composed of  $\alpha$  and  $\beta$  segments. (c)  $\beta$  segments being removed to yield irregular shape Figure 2a.

When using the desegmentation method, the Green's function is evaluated for the  $\gamma$  segment in Figure 3(b) and the impedance response of the  $\beta$  segments is removed. The  $\beta$  segments must be regular patterns for which Green's functions are available. The application and extension of the desegmentation technique is the focus of this work. The results generated by the desegmentation technique provide an impedance matrix or scattering matrix capable of describing inductor patterns over a wide frequency range.

Accurate inductor modeling is of great interest to analog circuit designers. Physical models typically include lumped elements [5] to combine the parasitics present from on chip fabrication with the series inductance of the designed inductor. Series inductance ( $L_S$ ), inner turn capacitance ( $C_S$ ), series resistance ( $C_S$ ), oxide capacitance ( $C_S$ ), silicon substrate capacitance ( $C_S$ ), and silicon substrate resistance ( $C_S$ ) are considered in the lumped element model shown in Figure 4(a).

Figure 4. (a) Lumped element model of on chip spiral inductor. (b) Z matrix representation.

The equivalent circuit for Figure 4(a) could be represented as a Z or S matrix. Either form can provide accurate characterization of integrated inductors for use in analog circuit design. The level to which coupling parasitics are included determines the overall accuracy and validity of the lumped element model. The technique used in this study

allows for the direct calculation of impedance parameters from a Green's function for rectangular microstrip cavities.

#### 3.2 Mathematical Formulation

Desegmentation has been previously developed to address the removal of a single segment [21] - [22]. To apply the desegmentation method, a technique to determine impedance must be selected. In this study, rectangular geometries are considered and impedance parameters are found using Green's functions for a rectangular cavity. For thin dielectrics (dielectric thickness, d <<λ), the analytical model for the cross section in Figure 1(c) is based on the application of the cavity model. The cavity model assumes perfect electric walls at the metal dielectric interfaces and perfect magnetic sidewalls on the vertical sides, which are perpendicular to the perfect electric conductors. Ports can be defined arbitrarily within the cavity where current is excited perpendicular to the surface of the conductor. The cavity model leads to the electromagnetic solution as a Green's function. The cavity model provides impedance results for regular patterns and the segmentation or desegmentation techniques are used to extend the closed form solution for irregular patterns. The desegmentation technique is considered here and extended to allow for multiple segment removal.

#### 3.2.1 Green's Function for Rectangular Geometries

Figure 5(a) shows a microstrip cavity with perfect electric conductors (PEC) on the top and bottom, as well as perfect magnetic conductors (PMC) on the vertical sidewalls. The dielectric thickness is d, a is the x dimension length, b is the y dimension

length,  $W_{xi}$  is the x dimension width of the ith port,  $W_{yi}$  is the y dimension width of the ith port,  $W_{xj}$  is the x dimension width of the jth port,  $W_{yj}$  is the y dimension width of the jth port,  $\mu_r$  is the relative permeability,  $\epsilon_r$  is the relative permittivity, and  $\tan(\delta)$  is the dielectric loss tangent. Figure 5(b) shows the port placement where  $x_i$  is the center x position of port i,  $x_j$  is the center x position of port j,  $y_i$  is the center y position of port i, and  $y_j$  is the center y position of port j.

Figure 5. (a) Microstrip cavity showing port definitions. (b) Plan view of microstrip cavity showing port definitions.

The impedance for a rectangular microstrip segment is expressed using Green's function in (1) [23].

$$Z_{ij} = \frac{1}{W_{xj}W_{xi}W_{yj}W_{yi}} \int_{W_{xi}W_{xj}} \int_{W_{yi}W_{yj}} \int_{W_{yj}} G(x, y | x_o, y_o) dx dx_o dy dy_o$$

$$\tag{1}$$

where  $W_i$  and  $W_j$  are the widths of ports i and j respectively and  $G(x,y|x_o,y_o)$  is a Green's function. To describe the electromagnetic condition in the cavity of Figure 5(a), the Helmholtz equation (2) is used.

$$\nabla^2 E_z + k^2 E_z = j \omega \mu I_z \tag{2}$$

$E_Z$  is z component of the electric field,  $\omega$  is the angular frequency equal to  $2\pi f$ ,  $\mu$  is the permeability  $(\mu_r \mu_o)$ , k is the wave number, and  $I_Z$  is the current directed in the z direction. For thin cavities  $(d << \lambda)$  the electric field is found by dividing the voltage by the dielectric thickness as shown in (3).

$$E_{\mathcal{Z}} = \frac{V_{\mathcal{Z}}}{d} \tag{3}$$

The voltage variation on the microstrip cavity can be determined by defining the voltage response as a Green's function due to a current excitation  $\delta$  as seen in (4).

$$\left(\nabla^2 + k^2\right) G(x, y; x', y') = j\omega\mu d\delta(x - x')\delta(y - y') \tag{4}$$

The Green's function can be expressed in series form (5),

$$G(x, y; x', y') = \sum \frac{j \omega \mu d \psi_{mn}(x, y) \psi_{mn}(x', y')}{\left(k_{mn}^2 - k^2\right)}$$

$$(5)$$

where  $\Psi_{mn}$  and  $k_{mn}$  are the eigenfunctions and eigenvalues respectively.

By applying the electric and magnetic wall boundary conditions described in Figure 5(a), the Green's function is shown in (6) [23].

$$G(x_i, y_i; x_j, y_j) = \frac{j \alpha \mu d}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_m^2 \varepsilon_n^2}{k_x^2 + k_y^2 - k^2} \times \cos(k_x x_i) \cos(k_x x_j) \cos(k_y y_i) \cos(k_y y_j)$$

$$(6)$$

where

$$k_X = \frac{m\pi}{a}$$

,  $k_Y = \frac{n\pi}{b}$ ,  $\varepsilon_m = \begin{cases} 1 & m=0 \\ \sqrt{2} & m \neq 0 \end{cases}$ , and  $\varepsilon_n = \begin{cases} 1 & n=0 \\ \sqrt{2} & n \neq 0 \end{cases}$ .

The wave number is.

$$k = k' - jk'' = \varpi \sqrt{\mu \varepsilon} - j\varpi \sqrt{\mu \varepsilon} \frac{\tan(\delta) + \frac{r}{d}}{2}$$

(7)

where,

$$r = \frac{1}{\sqrt{\pi f \mu \sigma}} \tag{8}$$

By applying k'', the loss contributed from the finite metal conductivity ( $\sigma$ ) and dielectric loss (tan( $\delta$ )) can be accounted for. Using (1) and (6), the impedance between ports can be found and is expressed in (9) [23].

$$Z(x_{i}, y_{i}; x_{j}, y_{j}) = \frac{j\omega\mu d}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_{m}^{2} \varepsilon_{n}^{2}}{k_{x}^{2} + k_{y}^{2} - k^{2}} \times \cos(k_{x}x_{i})\cos(k_{x}x_{j})\cos(k_{y}y_{i})\cos(k_{y}y_{j}) \times \sin\left(\frac{k_{x}W_{xi}}{2}\right) \operatorname{sinc}\left(\frac{k_{x}W_{xj}}{2}\right) \operatorname{sinc}\left(\frac{k_{y}W_{yj}}{2}\right) \operatorname{sinc}\left(\frac{k_{y}W_{yj}}{2}\right)$$

$$(9)$$

(9) can be applied to rectangular cavities and is used in combination with the desegmentation method to provide solutions to circuit patterns consisting of regular shapes.

#### 3.2.2 Single Segment Removal

The desegmentation method has been proposed and developed in [21]-[22]. In contrast to segmentation, desegmentation subtracts segments for which (9) can be applied from other regularly shaped segments. To illustrate the capability of the desegmentation technique, the ring pattern in Figure 6 is considered.

Figure 6. (a) Rectangular ring pattern. (b) Application of segmentation. (c) Application of desegmentation.

It can be seen that when segmentation is applied to the pattern in Figure 6(a), the addition of  $S_1,S_2,S_3$  and  $S_4$  will result in the desired pattern. If desegmentation is applied, the effect of  $D_2$  is subtracted from  $D_1$ . If segmentation is used, (9) must be calculated for four segments, whereas desegmentation requires (9) to be applied on only two segments.

The development of desegmentation stems from the segmentation method for which Z matrices are used [20]. If a Green's function were available for the  $\alpha$  segment in Figure 7(a), segmentation in could be applied as shown in Figure 7.

Figure 7. Illustration of segmentation when  $Z_{pp}^{\ \alpha}$  can not be found. (a)  $\alpha$  segment. (b)  $\beta$  segment. (c)  $\gamma$  segment.

P is the number of externally connected ports  $(p_1,p_2...p_P)$ , while C  $(c_1,c_2,...c_C)$ , and D  $(d_1,d_2,...d_D)$  are the number of interconnected ports. C must equal D, and the necessary number of ports for convergence is dependent on frequency. Using the segmentation method outlined in [20], impedance matrices can be used to determine  $Z_{pp}^{\gamma}$  as shown in [21].

$$Z_{pp}^{\gamma} = Z_{pp}^{\alpha} - Z_{pc}^{\alpha} \left[ Z_{cc}^{\alpha} + Z_{dd}^{\beta} \right]^{-1} Z_{cp}^{\alpha}$$

(10)

$Z_{cc}{}^{\alpha}$ ,  $Z_{pc}{}^{\alpha}$ , and  $Z_{cp}{}^{\alpha}$  can not be found directly, however, if a Green's function is known for the  $\gamma$  and  $\beta$  segments, the  $\alpha$  matrices can be found in terms of the impedance matrices for the  $\gamma$  and  $\beta$  segments. If D is set equal to C and renamed to Q, the desegmentation formula can be rearranged as (11) [21].

$$Z_{pp}{}^{\alpha} = Z_{pp}{}^{\gamma} - Z_{pq}{}^{\gamma} \left[ Z_{qq}{}^{\gamma} - Z_{qq}{}^{\beta} \right]^{-1} Z_{qp}{}^{\gamma}$$

(11)

The Q and P ports are placed as shown in Figure 8.

Figure 8. Desegmentation method applied as expressed in (11).

As with the segmentation method, P ports are externally connected ports. Q ports, however, serve as internally connected ports on the  $\gamma$  segment and externally connected ports on the  $\beta$  segment. The number of Q ports on the perimeter of the  $\beta$  segment can be increased thereby decreasing the width of these ports. This is normally done until the solution converges to an acceptable level.

$Z_{pp}^{\ \alpha}$  is the impedance between the p ports on the irregularly shaped  $\alpha$  segment.  $Z_{pq}^{\ \gamma}$  is the impedance between the p and q ports on the regularly shaped  $\gamma$  segment.  $Z_{qq}^{\ \gamma}$  is the impedance between the p and p ports on the regularly shaped  $\gamma$  segment.  $Z_{qp}^{\ \gamma}$  is the impedance between the q and p ports on the regularly shaped  $\gamma$  segment.  $Z_{qq}^{\ \gamma}$  is the impedance between the q ports on the regularly shaped  $\gamma$  segment.  $Z_{qq}^{\ \beta}$  is the impedance between the q ports on the regularly shaped  $\beta$  segment. Each port is defined in terms of center x position, center y position, x width, and y width. In order to apply (9) the port placement must be defined along with the dimensions of the rectangles being analyzed  $(x_i, x_j, W_{xi}, W_{yi}, W_{xj}, W_{yj}, a, b)$ .

Figure 9. (a) Port definition for  $Z_{pp}^{\gamma}$ . (b) Port definition for  $Z_{pq}^{\gamma}$ . (c) Port definition for  $Z_{qq}^{\gamma}$ . (d) Port definition for  $Z_{qq}^{\gamma}$ .

Calculating  $Z_{pp}^{\gamma}$  shown in Figure 9(a):

For element  $Z_{11}$  in  $Z_{pp}^{\ \ \gamma}$ , (9) is applied where:

$x_i = x_{i,j}, x_j = x_{i,j}, W_{xi} = W_{xj} = W_{xi,xj}, W_{yi} = W_{yj} = W_{yi,yj}, a=A, b=B as shown in Figure 9(a).$

Calculating  $Z_{pq}^{\gamma}$  shown in Figure 9(b):

For element  $Z_{11}$  in  $Z_{pq}^{\gamma}$ ,  $x_i=x_i$ ,  $x_j=x_{1j}$ ,  $W_{xi}=W_{xi}$ ,  $W_{yi}=W_{yj}$ ,  $W_{xj}=0$   $W_{yj}=b$ , a=A, b=B as shown in Figure 9(b).

For element  $Z_{12}$  in  $Z_{pq}^{\gamma}$ ,  $x_i=x_i$ ,  $x_j=x_{2j}$ ,  $W_{xi}=W_{xi}$ ,  $W_{yi}=W_{yj}$ ,  $W_{xj}=a$ ,  $W_{yj}=0$ , a=A, b=B as shown in Figure 9(b). Similarly,  $Z_{13}$  and  $Z_{14}$  for  $Z_{pq}^{\gamma}$  can be found.

$Z_{qp}^{\ \gamma}$  can be determined a similar manner or a transpose of  $Z_{pq}^{\ \gamma}$  can be done to reduce computing time.

Calculating  $Z_{qq}^{\gamma}$  shown in Figure 9(c):

For element  $Z_{11}$  for  $Z_{qq}^{\gamma}$ ,  $x_i=x_{1i}$ ,  $x_j=x_{1i}$ ,  $W_{xi}=0$ ,  $W_{yi}=b$ ,  $W_{xj}=0$   $W_{yj}=b$ , a=A, b=B as shown in Figure 9(c).

For element  $Z_{12}$  for  $Z_{qq}^{\ \gamma}$ ,  $x_i = x_{1i}$ ,  $x_j = x_{2j}$ ,  $W_{xi} = 0$ ,  $W_{yi} = b$ ,  $W_{xj} = a$ ,  $W_{yj} = 0$ , a = A, b = B as shown in Figure 9(c). Similarly,  $Z_{13}$ ,  $Z_{14}$ ,  $Z_{21} \to Z_{24}$ ,  $Z_{31} \to Z_{34}$ ,  $Z_{41} \to Z_{44}$  for  $Z_{qq}^{\ \gamma}$  can be found.

Calculating  $Z_{qq}^{\beta}$  shown in Figure 9(d):

For element  $Z_{11}$  for  $Z_{qq}^{\beta}$ ,  $x_i=x_{1i}$ ,  $x_j=x_{1i}$ ,  $W_{xi}=0$ ,  $W_{yi}=b$ ,  $W_{xj}=0$   $W_{yj}=b$ , a=A, b=B as shown in Figure 9(c).

For element  $Z_{12}$  for  $Z_{qq}{}^{\beta}$ ,  $x_i = x_{1i}$ ,  $x_j = x_{2j}$ ,  $W_{xi} = 0$ ,  $W_{yi} = b$ ,  $W_{xj} = a$ ,  $W_{yj} = 0$ , a = a, b = b as shown in Figure 9(d). Similarly,  $Z_{13}$ ,  $Z_{14}$ ,  $Z_{21} \to Z_{24}$ ,  $Z_{31} \to Z_{34}$ ,  $Z_{41} \to Z_{44}$  for  $Z_{qq}{}^{\beta}$  can be found.

Once  $Z_{pp}^{\gamma}$ ,  $Z_{pq}^{\gamma}$ ,  $Z_{qp}^{\gamma}$ ,  $Z_{qq}^{\gamma}$  and  $Z_{qq}^{\beta}$  are known, (11) can be used to determine  $Z_{pp}^{\alpha}$ , or the impedance matrix for the irregular shape shown in Figure 8 ( $\alpha$  pattern). It is also possible to add additional q ports around the perimeter of the segment to be removed. Doubling the number of q ports reduces the width of the q ports by 50%. By reducing the length of the q ports around the perimeter of the  $\beta$  segment, greater accuracy can be obtained.

# 3.2.3 Convergence Analysis for Single Segment Removal

The convergence behavior of the desegmentation technique for single segment removal described in 3.2.2 is presented to illustrate the steps necessary to obtain a

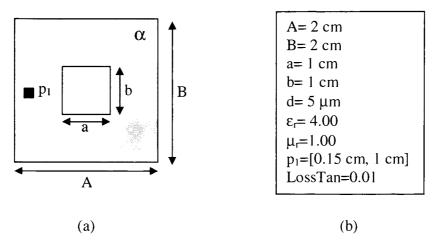

solution of desired accuracy. The presence of the double summations in (9) allows higher order modes to be discarded when they are insignificant for a particular set of dimensions. The number of m and n modes necessary for convergence is dependent upon the frequency on interest. For relatively low frequencies, fewer eigenmodes are required than for relatively higher frequencies. Consequently, objects with longer physical lengths require a greater number of modes to be summed. The convergence study presented in 3.2.3 investigates the convergence characteristics for the symmetric rectangular ring pattern shown in Figure 10(a). By symmetry, eigenmodes m and n will be set to have equal values.

The procedure for determining convergence involves three parameters: m eigenmodes in the x direction, n eigenmodes in the y direction, and q port width.  $S_{11}$  [dB] vs. frequency for a single external p port has been calculated, and the first two resonant frequencies (minimum  $S_{11}$  [dB]) are determined. As m and n are increased, the change in the resonant frequencies ( $\Delta f_r$ ) is noted. After achieving the desired convergence through the increase in eigenmodes, the width of the q ports is decreased. The resonant frequencies are again inspected as the port width is reduced. The numerical example in Figure 10(b) is considered. The assigned dimensions and material parameters are shown in Figure 10(b).

Figure 10. (a) Pattern tested for convergence. (b) Dimensions and material parameters.

Using the desegmentation method, convergence data has been collected using single segment removal. The change in resonant frequency,  $\Delta f_r$ , is found by calculating the shift in the resonant frequency when additional modes are included in the double summation of (9). Each data point in Figure 12 contains two additional m and n eigenmodes relative to the previous data point. 4 q ports are evenly distributed around the inner  $\beta$  segment for the eigenmode convergence test.

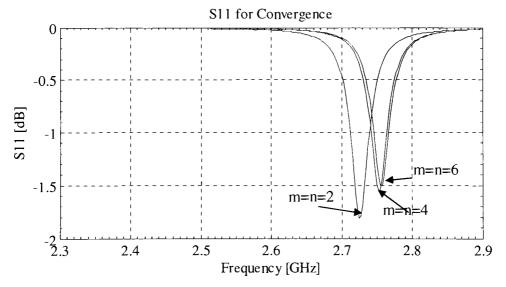

Figure 11. Eigenmode convergence for  $S_{11}$  for ring pattern.

Figure 12. (a) Change in first two resonant frequencies  $(f_{r1}, f_{r2})$  vs. n and m eigenmodes.

After m=n=34 for and 16 q ports are placed, the first two resonant frequencies are,

$$f_{r1} = 2.76 \text{ GHz}$$

$f_{r2} = 5.84 \text{ GHz}$

Once the change in frequency is less than equal to 10MHz (<1%), the process is halted and the solution is converged to the desired degree.

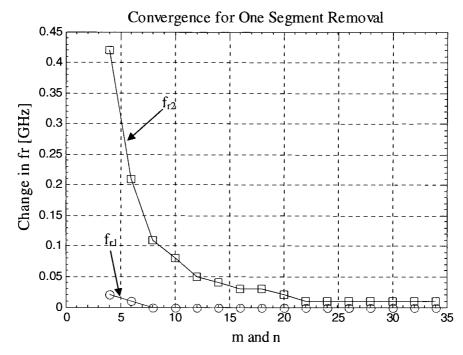

Next, m and n are set to 34 and the number of q ports is increased, thereby reducing the width of the q ports.

Figure 13. First resonant frequency vs. q port width (m=n=34).

Figure 14. Second resonant frequency vs. q port width (m=n=34).

As the port width is decreased, the converged resonant frequency is approached. The resonant frequency is obtained by noting where the change in resonant frequency fell below the specified tolerance, in this case 10 MHz (<1% of  $f_r$ ). The first resonant frequency converged with a port width of 5 mm while the second resonant frequency

converged with a port width of 2 mm. Higher frequencies require a reduced port width.

The final resonant frequencies are:

$$f_{r1} = 2.69 \text{ GHz}$$

$f_{r2} = 5.81 \text{ GHz}$

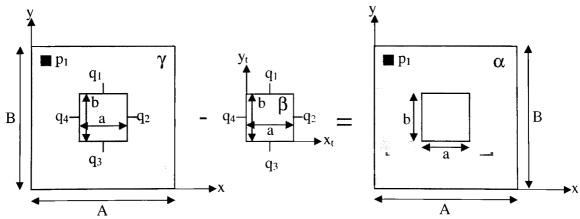

## 3.2.4 Two Segment Removal

In order to remove two pieces using the desegmentation method, it is proposed that additional fictitious p ports be placed around the periphery of the additional segment to be removed. For comparison, the rectangular ring in Figure 10(b) is analyzed by dividing the center segment into two segments.

Figure 15. (a) Initial  $\gamma$  segment ( $\gamma_1$ ). (b)  $\beta_1$  segment. (c)  $\alpha_1$  or  $\gamma_2$  segment. (d)  $\beta_2$  segment. (e) Final  $\alpha$  segment  $\alpha_2$ . (f) Physical parameters of rectangular ring under analysis.

The calculation of the first  $\alpha$  circuit in Figure 15 is done in the similar manor described in 3.2.2. For the removal of a second piece, additional fictitious p ports (p<sub>2</sub>-p<sub>5</sub>) are placed as shown in Figure 15(a). The fictitious p ports are defined in the same way as q ports. After the removal of the first  $\beta$  segment, the matrix that describes Figure 15(c) comes directly from (11). For four q ports per  $\beta$  segment, (12) is calculated. The  $\alpha$ 1 segment contains only p-ports. The  $\gamma$ 2 segment redefines the p ports around the  $\beta$ 2 segment to q ports (p<sub>2</sub>-p<sub>5</sub> to q<sub>5</sub>-q<sub>8</sub>).

$$Z_{pp}^{\alpha l} = \begin{bmatrix} Z_{11} & Z_{12} & Z_{13} & Z_{14} & Z_{15} \\ Z_{21} & Z_{22} & Z_{23} & Z_{24} & Z_{25} \\ Z_{31} & Z_{32} & Z_{33} & Z_{34} & Z_{35} \\ Z_{41} & Z_{42} & Z_{43} & Z_{44} & Z_{45} \\ Z_{51} & Z_{52} & Z_{53} & Z_{54} & Z_{55} \end{bmatrix}$$

(12)

The submatrices of (12) make up  $Z_{pp}^{\gamma 2}$ ,  $Z_{pq}^{\gamma 2}$ ,  $Z_{qp}^{\gamma 2}$ , and  $Z_{qq}^{\gamma 2}$  as shown in (13).

$$Z_{pp}^{\alpha l} = \begin{bmatrix} Z_{pp}^{\gamma 2} & \leftarrow & Z_{pq}^{\gamma 2} & \rightarrow \\ \uparrow & & \uparrow & \\ Z_{qp}^{\gamma 2} & \leftarrow & Z_{qq}^{\gamma 2} & \rightarrow \\ \downarrow & & \downarrow & \end{bmatrix}$$

$$(13)$$

From this point,  $Z_{pp}^{\gamma 2}$ ,  $Z_{pq}^{\gamma 2}$ ,  $Z_{qp}^{\gamma 2}$ , and  $Z_{qq}^{\gamma 2}$  are known and  $Z_{qq}^{\beta 2}$  is found directly by using (9). (11) is then applied again to determine  $Z_{pp}^{\alpha 2}$  in Figure 15(e).

## 3.2.5 Convergence Analysis for Double Segment Removal

For the parameters shown in Figure 15(f) convergence can be collected. First, the number of eigenmodes is increased until the change in the resonant frequency fell to an acceptable level (<10 MHz). Next, the number of q ports is increased until the solution converges. Since the number of q ports are evenly distributed on each side around the  $\beta$  segment, the q port width is taken to be the maximum q port width in each case.

Figure 16. Eigenmode convergence for two segment removal for the first two resonant frequencies.

Figure 16 shows how the first two resonant frequencies change as an increasing number of eigenmodes are summed. When m=n=34 and the q port width is equal to 1 cm, the first two resonant frequencies have been found as,

$$f_{r1} = 2.73 \text{ GHz}$$

$f_{r2} = 5.86 \text{ GHz}$

Next, m and n are held constant at 34 as the q port width is decreased. The resonant frequency is found as a function of decreasing port width.

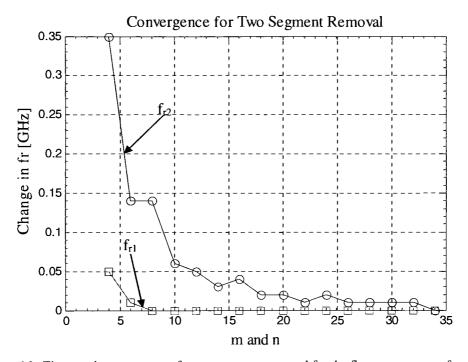

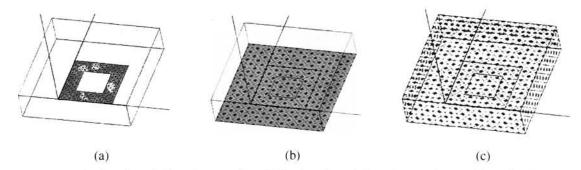

Figure 17. Convergence for first resonant frequency when two segments are removed (m=n=34).

Figure 18. Convergence for second resonant frequency when two segments are removed (m=n=34).

Figure 17 and Figure 18 show the response in the first and second resonant frequencies respectively, vs. decreasing q port width for two segment removal. After the reduction of

the port width to 1.67 mm shown in Figure 17 and Figure 18, the resonant frequencies are found as:

$$f_{r1} = 2.69 \text{ GHz}$$

$f_{r2} = 5.84 \text{ GHz}$

Increasing m and n to 80 when the q port width is set to 1.67 mm eliminated the 0.03 GHz difference between the single and double segment removal for the second resonant frequency. The final solutions found using double segment removal are:

$$f_{r1} = 2.69 \text{ GHz}$$

$f_{r2} = 5.81 \text{ GHz}$

It is evident that multiple segment removal exhibits slightly different convergence characteristics than single segment removal. In two segment removal, as the number of q ports is increased, additional eigenmodes are necessary for convergence. The single segment removal and the double segment removal each yielded a fr<sub>1</sub>=2.69 GHz and fr<sub>2</sub>=5.81 GHz, where the values are found to the nearest 10 MHz. The solution for one segment removal converged with m=n=34 and a q port width of 1.67 mm, while two segment removal required m=n=100 and a q port width of 1.67 mm for similar convergence.

#### 3.2.6 N Segment Removal

The process in 3.2.4 can be extended to handle the removal of N number of segments. After one segment is removed, (14) is calculated using (11).

$$Z_{pp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} \\ Z_{21} & Z_{22} & \cdots & Z_{2(n-k)} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{(n-k)1} & Z_{(n-k)2} & \cdots & Z_{(n-k)(n-k)} & \cdots & Z_{(n-k)n} \\ \vdots & \vdots & \ddots & \vdots & \ddots & \vdots \\ Z_{n1} & Z_{n2} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{2n} \\ Z_{2n-k} & \cdots & Z_{2n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{1n} \\ Z_{2n} & \cdots & Z_{2n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} & \cdots & Z_{nn} \end{bmatrix}$$

$$Z_{qp}^{\gamma^{2}} = \begin{bmatrix} Z_{11} & Z_{12} & \cdots & Z_{1n} & \cdots & Z_{1n} \\ Z_{2n} & \cdots & Z_{2n} & \cdots & Z_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ Z_{n(n-k)} & \cdots & Z_{nn} & \cdots & Z_{nn} \end{bmatrix}$$

where n is the total number of p ports and the k is the number of Q ports per segment -1. Each time a segment is removed and an intermediate  $\alpha$  matrix is found, the p-ports on the subsequent segment to be removed are redefined to q ports, which forms the subsequent  $\gamma$  segments ( $\alpha$  is converted to  $\gamma$ ).  $Z_{qq}^{\beta}$  for the subsequent segment can be found directly and (11) can be applied again. This process is repeated for all segments that are to be removed until the final pattern is achieved. (15) is used for extracting the intermediate  $Z^{\gamma}$  parameters, where x is the segment number being removed, and  $Z_{pp}^{\gamma}, Z_{pq}^{\gamma}, Z_{qp}^{\gamma}$  and  $Z_{qq}^{\gamma}$  are the sub matrices from (14).

$$Z_{pp}^{\alpha(x)} = \begin{bmatrix} Z_{pp}^{\gamma(x+1)} & Z_{pq}^{\gamma(x+1)} \\ Z_{qp}^{\gamma(x+1)} & Z_{qq}^{\gamma(x+1)} \end{bmatrix}$$

(15)

The convergence analysis can be carried out in a similar manner as done in 3.2.5.

# 4. Numerical Modeling

Numerical EM full wave solvers typically require more calculations than simplified analytical models but have greater flexibility for solving a larger variety of problems. Numerical modeling tools also assist in the validation of analytical modeling technique by providing a standard for comparison.

### 4.1 Available Numerical Modeling Tools

Ansoft HFSS and Maxwell 3D are two modeling tools that provide the electromagnetic response to a given excitation. High frequency structure simulator (HFSS) accounts for high frequency effects that become significant as the wavelength of the excitation approaches the physical dimensions of the circuit under investigation.

#### 4.2 HFSS

HFSS allows for the geometric definition and analysis of structures in a 3D environment. In addition, layouts from other software packages can be directly imported for electromagnetic analysis.

#### 4.2.1 Structure Definition in HFSS

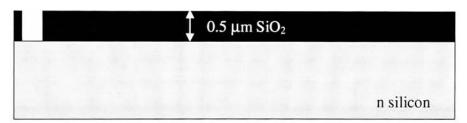

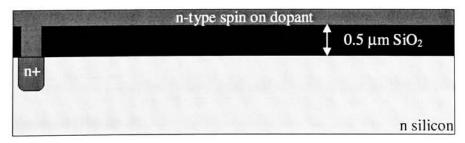

The pattern shown in Figure 19 is investigated. For analytical comparison, perfect electric walls are defined for the signal trace and the ground plane in HFSS. The dielectric is given a permittivity, permeability, and a loss tangent. The loss tangent is provided to yield finite impedances at resonant frequencies.

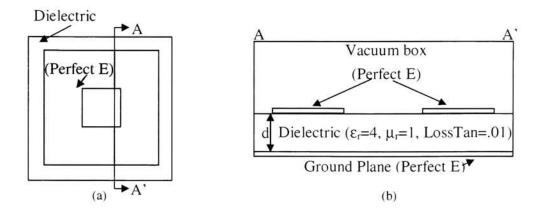

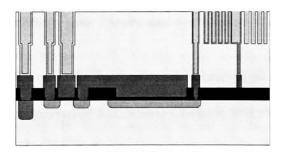

Figure 19. (a) Plan view of a rectangular ring. (b) Cross section of rectangular ring.

When the pattern in Figure 19 is defined in HFSS, 2-dimensional rectangles are used to define the top ring pattern and a perfect electric conductor boundary condition is assigned. A 3-dimensional box is defined with a thickness of d and is extended beyond the ring pattern. The dielectric characteristics are provided to this box which is positioned under the ring pattern. A perfect electric conductor boundary is assigned to the bottom face of the dielectric box to provide a ground plane. A 3-dimensional box is placed above the surface of the dielectric and assigned the electrical properties of vacuum  $(\mu_r=1, \epsilon_r=1, lossless)$ . Radiation boundaries are assigned to the 5 outer perimeter faces of the vacuum box.

Figure 20. (a) Perfect electric boundary on ring. (b) Perfect electric boundary on bottom face of dielectric. (c) Radiation boundaries on 5 outer faces of vacuum box.

The thickness of the metal used for the ground plane and ring pattern are not accounted for in the cavity model. When perfect electric boundaries are specified in HFSS, the thickness and loss presented by the metallic layers are neglected.

#### 4.2.2 Port Definition in HFSS

To define an excitation within the cavity, a lumped port is used. The lumped port can be defined anywhere within the structure, which provides flexibility in port placement. First, a placement rectangle is drawn from the signal trace to the ground plane where an excitation port is desired. Next, a lumped port is placed in the center of the placement rectangle by drawing an integration line from the signal trace to the ground plane in the center of the placement rectangle. The impedance of the port can be set in order to match any test equipment being used.  $50 \Omega$  is used for all lumped ports for the calculation of the S parameters in this study.

Figure 21. (a) Angle view of rectangular ring. (b) Zoom of port placement.

The 50  $\Omega$  lumped port can be seen in Figure 21(b). Figure 21(b) shows a zoom view of the picture in Figure 21(a).

## 4.2.3 Analysis Setup in HFSS

All simulations are performed using the driven modal solution type. The analysis setup is set to have a solution frequency at least  $\frac{3}{4}$  of the highest frequency of interest. The convergence parameter for maximum  $\Delta S$  per pass is adjusted for each simulation to yield accurate results. When solutions are collected over a range of frequencies, a discrete sweep is done to maintain accuracy.

# 5. Comparison of Analytical and Numerical Techniques

The analytical technique of desegmentation has been programmed in MATLAB to provide results and comparison to simulated HFSS results.

## 5.1 Rectangular Ring

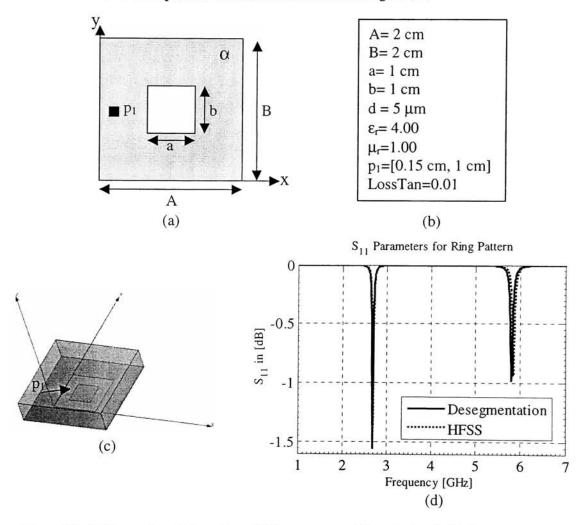

The ring pattern discussed in 3.2.4 is analyzed using HFSS and desegmentation. The boundaries are set up in the same manner shown in Figure 20.

Figure 22. (a) Planar view of ring pattern. (b) Parameters used for analysis. (c) HFSS capture of ring pattern. (d) S<sub>11</sub> for ring pattern.

Figure 22 shows the characteristics of the simulated structure. The parameters for the convergence of the analytical model include m=n=35 and a q port width equal to 1.67 mm (24 q ports). Single segment removal has been applied.

For HFSS, perfect electric conductor walls are defined on the signal trace and on the ground plane. A port placement rectangle is placed at (0.15cm, 1.0cm) with a width of 0  $\mu$ m in the y direction, 1  $\mu$ m in the x direction, and 5  $\mu$ m (thickness of dielectric) in the z direction. A lumped port is defined by placing an integration line down the center of the placement rectangle. The solution frequency is equal to 7 GHz, the max  $\Delta$ S<.0002, and a discrete sweep has been done from 1 GHz to 7 GHz in steps of 0.01 GHz.

| S <sub>11</sub> Results (Figure 22) | HFSS     | Desegmentation | % Difference |  |

|-------------------------------------|----------|----------------|--------------|--|

| $f_{r1}$                            | 2.69 GHz | 2.69 GHz       | 0.0%         |  |

| $f_{r2}$                            | 5.84 GHz | 5.81 GHz       | 0.5%         |  |

Figure 23. Table of resulting resonant frequencies for pattern in Figure 22.

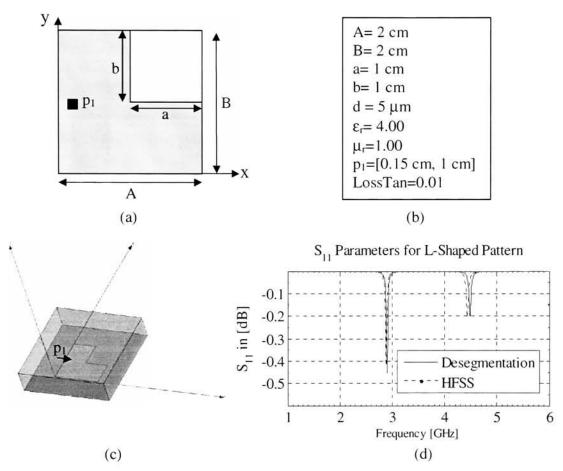

## 5.2 L- Shaped Plane

An L shaped pattern has been analyzed and the resonant frequencies are found using HFSS and the desegmentation technique. Single segment removal is applied to the L-shaped pattern for analytical calculations. The parameters for the convergence of the desegmentation model included m=n=20 and a q port width equal to 3.33 mm (12 ports).

For HFSS, perfect electric walls are defined on the signal trace and on the ground plane. A port placement rectangle is placed at (0.15cm, 1.0cm) with a width of 0  $\mu$ m in the y direction, 1  $\mu$ m in the x direction, and 5  $\mu$ m (thickness of dielectric) in the z

direction. A lumped port is defined by placing an integration line down the center of the placement rectangle. The solution frequency is equal to 4.40 GHz, the max  $\Delta$ S<0.004, and a discrete sweep has been done from 1 GHz to 6 GHz in steps of 0.01 GHz.

Figure 24. (a) Planar view of L-shaped pattern (b) Parameters used for analysis (c) HFSS capture of L shaped pattern (d) S<sub>11</sub> for L-shaped pattern.

| S <sub>11</sub> Results (Figure 24) | HFSS     | Desegmentation | % Difference |

|-------------------------------------|----------|----------------|--------------|

| $f_{rl}$                            | 2.89 GHz | 2.905 GHz      | 0.5%         |

| $f_{r2}$                            | 4.44 GHz | 4.49 GHz       | 1.1%         |

Figure 25. Table of resulting resonant frequencies for pattern in Figure 24.

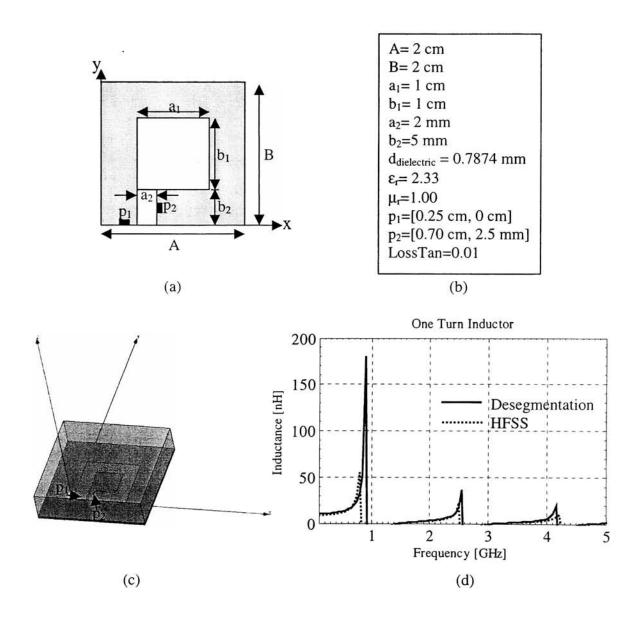

#### 5.3 One Turn Inductor

A one turn inductor is analyzed by using two segment desegmentation and HFSS.

The boundaries are again setup as described in Figure 20.

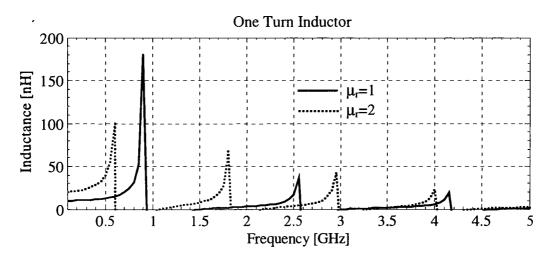

Figure 26. (a) Plan view of a one turn inductor pattern. (b) Parameters used for analysis. (c) HFSS capture of one turn inductor structure pattern. (d) Inductance for one turn inductor.

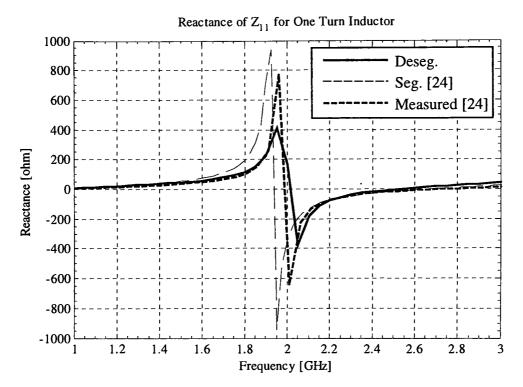

Figure 27. (a) Segmentation vs. desegmentation vs. measured data.

The desegmentation technique is applied to the one turn inductor shown in Figure 26 by removing two segments. The eignenmodes necessary for convergence are m=n=250. The maximum q port width used is 1.67 mm (24 q ports per segment). The analytical calculations are performed from 0.1 GHz to 5 GHz in steps of 50MHz. Figure 27 compares the segmentation technique from [24], measured data from [24], and modeled results from the desegmentation technique.

For HFSS, perfect electric conductor walls are defined on the signal trace and on the ground plane. Port placement rectangles are placed at (2.5 mm, 0.0 cm) and (7.0 mm, 2.5 mm) with a width of 0  $\mu$ m in the y direction, 1  $\mu$ m in the x direction, and 5  $\mu$ m (thickness of dielectric) in the z direction. A lumped port is defined by placing an integration line down the center of each placement rectangle. The solution frequency is

equal to 4.13 GHz, max  $\Delta$ S<.004, and a discrete sweep is done from 0.1 GHz to 5 GHz in steps of 50 MHz. Only the inductive regions are shown in Figure 26(d). The inductance for the one turn inductor in Figure 26 has been calculated from the impedance matrix by applying equation (16) [26].

$$L = \frac{im\left(Z_{11} - \frac{Z_{12}^2}{Z_{22}}\right)}{2\pi f}$$

(16)

| Data from (Figure 26) | HFSS     | Desegmentation | % Difference |

|-----------------------|----------|----------------|--------------|

| L [nH] (100MHz)       | 8.59 nH  | 10.14 nH       | 18%          |

| SRF <sub>1</sub>      | 0.84 GHz | 0.95 GHz       | 13%          |

| SRF <sub>2</sub>      | 2.52 GHz | 2.58 GHz       | 2.4%         |

| SRF <sub>3</sub>      | 4.24 GHz | 4.18 GHz       | 1.4%         |

Figure 28. Table of resulting inductance at 100MHz and SRF from Figure 26.

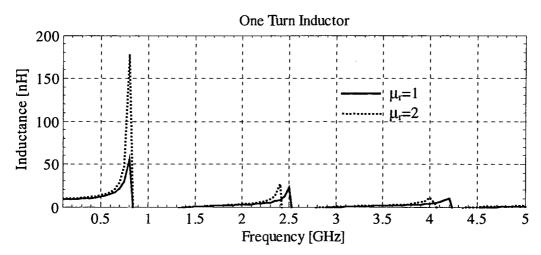

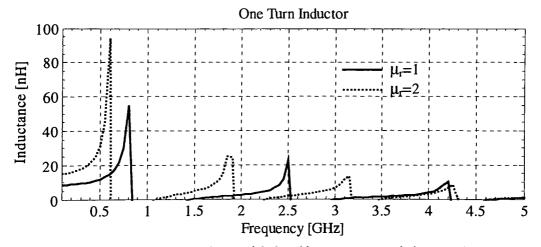

## 6. Ferrite Filled Inductors

For on chip inductors, the incorporation of a material with a  $\mu$ >1 allows for the enhancement of inductance without an increase in the footprint area. Ferrites can be used to enhance the permeability of the region around the inductor, and modify the electrical response over a range of frequencies. This modification can cause both desirable and undesirable effects. The modeling performed in this study is capable of addressing microstrip configurations where the inductor is located above a ground plane. The impedance of a microstrip cavity is shown in (9). The impedance is shown to be directly proportional to  $\mu$ . In addition, the frequency response of the impedance is divided by  $k^2$ , which is equal to  $(2\pi f)^2 \mu \epsilon$ . With an increase in  $\mu_r$ , the resonant frequencies will shift down. If an on chip inductor is immersed in a material with a  $\mu_r$ >1, the low frequency inductance will be increased however, the self resonant frequency will be decreased.

#### 6.1 Predicted Effect of Magnetic Material Filling Using HFSS

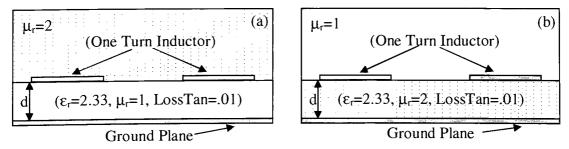

The inductor shown in Figure 26 (a) is modeled using HFSS and desegmentation. The inductance looking through the inductor is modeled and compared for the two different configurations shown in Figure 29.

Figure 29. (a) Magnetic material positioned above one turn inductor. (b) Magnetic material positioned between the inductor pattern and the ground plane.

The dimensions of the one turn inductor are listed in Figure 26 (b). The permeability of the medium above and below the inductor pattern is modified and the resulting inductances are calculated. For HFSS, a solution frequency of 4 GHz is used, with an ultimate max  $\Delta$ S<0.03. A frequency sweep is performed from 100 MHz to 5 GHz in discrete steps of 50 MHz.

Figure 30. HFSS results for magnetic material placed above one turn inductor.