# Large Area Monolayer Doping Development

Brian Novak, Rochester Institute of Technology, Department of Electrical and Microelectronic Engineering

Abstract— One of the challenges facing the semiconductor industry as the scale of transistors shrink into nanometer sizes is the creation of ultra-shallow junctions. Furthermore, device geometry is morphing from planar to 3-dimensional structures which increases the need for conformal ultra-shallow junctions. The industry has relied on ion implantation to push the boundary of semiconductor doping, however effects such as transient enhanced diffusion caused by lattice damaged by implantation have impeded the creation of the desired ultra-shallow junctions. A new technique known as monolayer doping is one strategy to help solve both ultra-shallow junction formation as well as conformal doping. Monolayer doping relies on a self-assembled monolayer of a dopant containing compound covalently bonded to the silicon lattice which is then driven into the silicon by a rapid thermal anneal. This technique has been demonstrated at Rochester Institute of Technology (RIT) previously on the small scale of pieces of wafers. To enhance the characterization of this technique the process was scaled up to accommodate full 6 inch wafers which can then be easily run through the RIT Semiconductor & Microsystems Fabrication Laboratory (SMFL). A container and process were developed which successfully doped 6 inch wafers when compared to previously collected data. The wafers were run through a standard process in the SMFL to create devices for characterization. Monolayer doping research at RIT now has an easier and faster means of doping wafers for any future research planned.

Index Terms—Monolayer Doping, Ultra-Shallow Junction, MLD, Conformal Doping

#### I. INTRODUCTION

S device dimensions shrink and move from planar to Athree-dimensional the need for low junction depths and conformal doping profiles has increased. Current techniques use ion implantation which damages the silicon lattice which leads to an effect known as transient enhanced diffusion which limits shallow junction [1]. A new technique known as monolayer doping (MLD) is a method to reduce defects and form shallow, and conformal, junctions. MLD has been successfully demonstrated to produce shallow junctions with high surface concentration at Rochester Institute of Technology (RIT). However, this success has only been demonstrated on small cleaved samples of silicon which has limited characterization to metrology tests such as four point probe, secondary ion mass spectroscopy (SIMS) and spreading resistance profilometry (SRP). Electrical characterization has been limited as fabricating devices using many lithography layers is challenging with pieces of a wafer. Therefore, a design and method of performing monolayer doping for a full

6" wafer was created which is the subject of this work. This allows for easy processing in the Semiconductor and Microsystems Fabrication Laboratory (SMFL) at RIT to create devices to study the monolayer doping characteristics.

#### II. THEORY

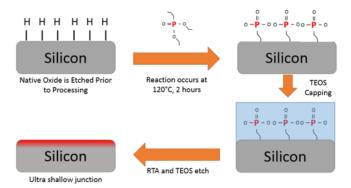

Monolayer doping was first reported in 2008 by Ho et al. from the University of Berkley [2]. It consists of the formation of self-assembled monolayers of a dopant containing molecule on the surface of crystalline silicon. A thermal anneal diffuses the dopants into the silicon. As seen in figure 1, the native oxide is removed from the silicon by hydrofluoric acid (HF), and reacted with the dopant containing molecules. The silicon is then capped with 50nm of (tetraethyl orthosilicate) TEOS and driven in with a rapid thermal anneal. The TEOS is removed with another HF bath.

Fig. 1. Monolayer doping diagram

The focus of this work is in the doping of phosphorus which is an n-type dopant. The chemistry used is diethyl 1-propylphosphonate. This is mixed in a 1:25 volume/volume ratio with Mesitylene, which is a solvent. This solvent is used to cheaply increase the volume of the chemistry.

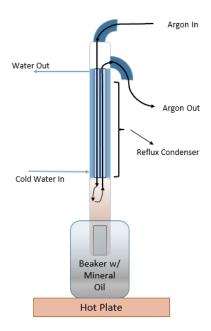

#### A. Apparatus for Pieces

The previous MLD experiments performed at RIT are shown in figure 2. The chemistry is measured out in a glove bag to keep the chemistry in an inert atmosphere. The chemistry is put into a test tube and sparged for 20 minutes. Sparging is the process by which inert gas is bubbled into the chemistry. This serves two purposes. It displaces any oxygen in the chemistry and also keeps the inert gas in the remainder of the test tube, keeping oxygen out of the ambient. The prepared wafer piece is put into the chemistry, and the test tube is connected to a reflux condenser. The tube is lowered into 120°C mineral oil and allowed to react for 2 hours.

The most important aspect of this system is the reflux condenser. It serves to bring argon into and out of the test tube, which keeps the ambient above the mixture inert. Secondly it is wrapped with a jacket for cold water to flow through. This allows for any vapors from the mixture to be condensed back, keeping the solution in a steady state.

Fig. 2. Apparatus for MLD on wafer pieces

# III. APPARATUS DESIGN

Looking at the apparatus used for wafer pieces in figure 2, a list of design ideas was proposed. The type of container needed, besides having to hold a 6-inch wafer, had to withstand the temperature of the experiment, as well as the solvent. To replicate the reflux condenser, it was decided that having an inlet and outlet for an inert gas to flow to maintain the inert environment would be best. It was also decided to condense any vapors, saving chemistry and keeping the solution in a steady state. With all designs, it was necessary to keep the chemistry volume used to a minimum and keep costs low.

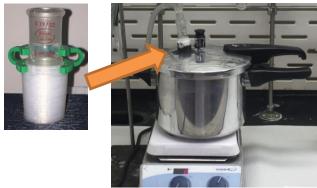

Again, looking at the apparatus, it became apparent that the reflux condenser met many of our design specifications. Therefore, it was decided to purchase a container to hold the wafers, and then decide how to connect the reflux condenser to it. The container purchased can be seen in figure 3, and is made from aluminum. It is designed to hold the wafer horizontally and can use as little as 200mL of total chemistry to submerge the single wafer.

Fig. 3. The purchased vessel for wafers

The task to connect the glass joint of the reflux condenser to the aluminum container was solved with 3D printing. A sleeve was designed and printed with a standard 3D printing filament: polylatic acid (PLA), as seen in figure 4. This was done as a prototype to ensure the correct sizing and fit, but would not be a long-term solution as PLA would be unable to withstand the temperature and chemistry.

Fig. 4. PLA printed sleeve for glass joint

To create a long-term solution a 3D filament of nylon was used, as this is much more temperature and chemically resistive. As seen in figure 5, the nylon sleeve was printed, and implanted into the system design.

This design was very low cost and meets all the design considerations that were specified. The container is able to withstand the temperature and chemistry, inert gas is allowed to flow into the chamber, and any vapors are condensed. Finally, it was very low cost, uses minimal volume, and will be very easy to replace parts.

Fig. 5. Nylon sleeve print and implementation

# IV. RESULTS AND ANALYSIS

#### A. Initial Results

The first run utilized 300mL of chemistry and a single 6" wafer. Leaks were discovered around the top of the container, which was later found to be due to a seal that was incompatible with the chemistry. This seal was replaced with room temperature vulcanized (RTV) silicone which has successfully run several more experiments.

However, even with the seal problem, the wafer was processed through the remaining MLD steps. It was capped with 40nm of TEOS and annealed at 1000°C for 5 minutes. Once the TEOS was removed, the sheet resistance was measured using the Resmap. As seen in table 1, the results of this measurement are consistent with sheet resistance measurements taken on pieces. It has been confirmed on wafer pieces that this sheet resistance is indicative of phosphorus doping.

TABLE I SHEET RESISTANCE MEASUREMENTS

|               | PRE-MLD $(\Omega/\Box)$                              | Post-MLD $(\Omega/\Box)$ |

|---------------|------------------------------------------------------|--------------------------|

| 6" Wafer:     | 213                                                  | 1126                     |

| Pieces:       | 191                                                  | 1031                     |

| Measured valu | les of sheet resistance compari<br>system implantati | C I                      |

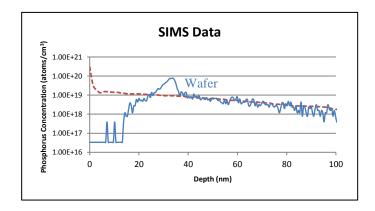

To ensure that phosphorus was doped on the 6-inch wafer, a sample was sent to the National Renewable Energy Laboratory (NREL) for secondary ion mass spectroscopy (SIMS) analysis. As seen in figure 6 Phosphorus was observed and reaches a similar background concentration as the historic data collected from wafer pieces. There is some discrepancy in the initial 30 nm of the collected data which is being investigated with NREL.

Fig. 6. Secondary ion mass spectroscopy data comparison between full 6-inch wafer (solid) and wafer piece (dashed)

## Piece

#### B. Anneal Time and Temperature Study

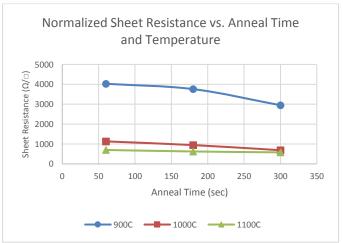

A benefit to doping full wafers is the ability to experiment in larger volumes than previously. This study involved varying the time and temperature of the anneal, measuring the sheet resistance and observing the effects. Ho et. al have performed this experiment also, and observed that as the temperature is increased the sheet resistance drops, and as the anneal time is increased, the sheet resistance also drops [2].

Figure 7 shows the results of three temperatures: 900°C, 1000°C and 1100°C at three different anneal times: 1 minute, 3 minutes and 5 minutes. It is observed that at 900°C that the sheet resistance is very high. This is attributed to phosphorus diffusing into the silicon, but not becoming active. The trends observed at 1000°C and 1100°C follow similar trends reported earlier, where sheet resistance is decreased as temperature and anneal time are increased.

Fig. 7. Resulting sheet resistance measured after varying anneal time and temperature

#### V. CONCLUSION

In order to better study the characteristics of monolayer doping a system was needed to dope full size wafers which can then be processed in the SMFL. Incorporating a key component from the system that wafer pieces were run through, the reflux condenser, kept the cost of a new system low. By purchasing a container to hold full 6" wafers and 3D

printing a nylon sleeve to attach the reflux condenser too further kept costs down. The system has worked as designed for several wafers. This was verified with sheet resistance measurements and secondary ion mass spectroscopy data which matched historically collected data. A study of the effects of annealing time and temperature shows that at 900°C the phosphorus dopant wasn't activating, but as the temperature and time were increased the sheet resistance measurements decreased. This was consistent with theory, as well as verified by previous publications on the subject.

# VI. FUTURE WORK

The creation of a system that dopes full 6" wafers has opened the door for many research opportunities at RIT. Besides modeling the doping process, doping of boron can now be performed on full wafers. The incorporation of MLD in the student run CMOS for source/drain and polysilicon gate doping can be investigated. MLD, as a conformal doping technique, could be used to conformally dope FinFETs. The photovoltaics industry could benefit from research of MLD as a selective emitter process. The investigation of through-silicon via doping has also been discussed.

# ACKNOWLEDGEMENT

The author would like to thank Dr. Santosh Kurinec and Dr. Scott Williams for all their guidance on this project as well as MS student Astha Tapriya for all her knowledge of the MLD process, BS student Daniel Shyer for owning a 3D Printer, the SMFL Staff for all their continuous help and guidance and David Young from the National Renewable Energy Laboratory.

# REFERENCES AND FOOTNOTES

# A. References

- [1] J. Ho, R. Yerushalmi, G. Smith, P. Majhi, J. Bennett, J. Halim, V. Faifer and A. Javey, "Wafer-Scale, Sub-5 nm Junction Formation by Monolayer Doping and Conventional Spike Annealing", Nano Letters, vol. 9, no. 2, pp. 725-730, 2009.

- [2] Ho, Johnny C., Roie Yerushalmi, Zachery A. Jacobson, Zhiyong Fan, Robert L. Alley, and Ali Javey. "Controlled Nanoscale Doping of Semiconductors via Molecular Monolayers." Nature Materials 7.1 (2007): 62-67. Web.

#### **AUTHOR**

Brian Novak is an undergraduate student in Microelectronic Engineering at RIT. He spent 2007-2011 touring as a monitor engineer for Robert Randolph and the Family Band before returning to school and in 2013 obtained an Associates of Applied Science Electrical Engineering Technology at Hudson Valley Community College. He has

held intern positions for Eastman Kodak and for Northrop Grumman.